# The Bang Bang PLL as a Clock Source in Serial-De-Serializer (SERDES) Applications

by

Raleigh Smith, BSc., MASc., P.Eng.

A dissertation submitted to the Faculty of Graduate and Postdoctoral Affairs in partial fulfillment of the requirements for the degree of

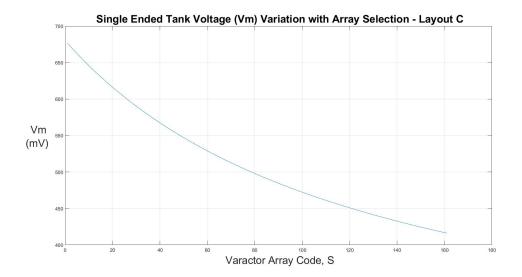

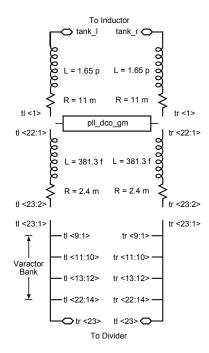

Doctor of Philosophy in Electrical and Computer Engineering

Ottawa-Carleton Institute for Electrical and Computer Engineering

Department of Electronics Engineering

Carleton University

Ottawa, Ontario

February, 2021

©Copyright Raleigh Smith, 2021

## Abstract

Demands for increased wireline data throughput necessitate multi-GHz clock sources of ever-greater fidelity. At the same time, there has been resolute industry pressure for process geometry size reduction, digital circuit implementation and modularization to fulfill the objectives of development cost reduction, scalability, increased functionality and decreased power dissipation.

In aid of these objectives, this work demonstrates a digital bang-bang phase-locked loop that develops the 14-GHz clock for a 56-Gb/s PAM-4 transceiver. This low jitter clock source is realized using an LC-based digitally-controlled oscillator having a frequency tuning range of 14 % and worst case resolution of 2.0 MHz/LSB. The major digital functions of the band-bang phase-locked loop are consolidated in a single, fully-synthesized digital signal processing unit operated at 3.5 GHz or 10x the reference clock frequency. Limit cycles are minimized, without the aid of a multibit time-to-digital-converter, through substantial reduction of loop latency using a look-ahead digital loop filter. Various design techniques exploiting an advanced 7-nm FinFET technology are discussed including noise reduction, frequency resolution and tank Q-enhancement. Additionally, methods of accurately modelling a digitally-controlled oscillator and linear loop analysis of the bang-bang phase-locked loop are demonstrated.

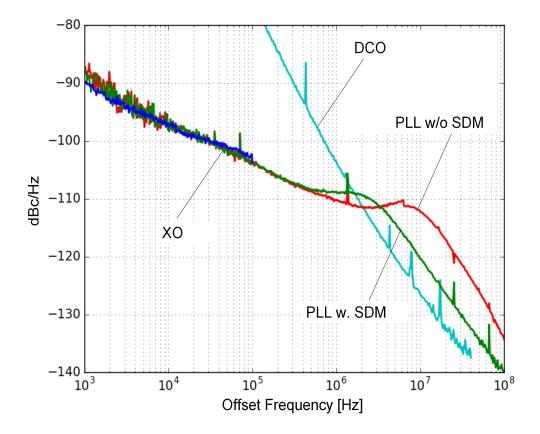

Closed-loop phase noise performance is accurately predicted using an industrystandard digital event-driven simulator with dramatically reduced computation effort compared to analogue or mixed-mode simulations. Here, a method of faithfully calculating various noise profiles for digitally-controlled and reference oscillators is exploited.

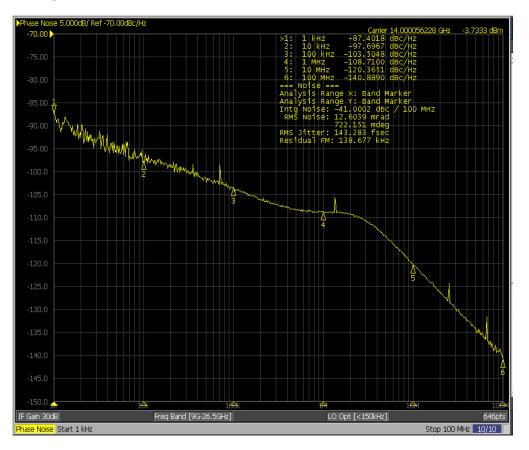

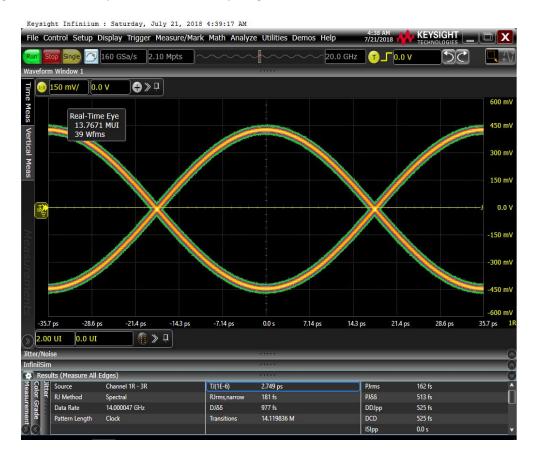

The measured RMS random jitter of the BBPLL, integrated from 1 kHz to 100 MHz, is 143 fs and shows limit-cycle free operation resulting in minimal spurious tone activity in the frequency spectrum. The BBPLL consumes 40 mW of power, while the DCO consumes 14.8 mW of this total. The RMS jitter demonstrated in

this thesis is consistent or better than analogue charge-pump PLLs of comparable frequency and significantly better than the reported BBPLLs at very competitive area and power dissipation.

To my parents, members in good standing of the Greatest Generation.

# Acknowledgments

I would to thank my supervisor, Prof. Ralph Mason, for his guidance, support and for securing the opportunity to carry out my PhD work with TSMC. His active participation in the success of this work is earnestly appreciated. Further to this, my deepest gratitude and thanks must go to Dr. Dirk Pfaff for his technical leadership, instruction and patient coaching throughout this whole project. His expectations and persistence pushed me further than I would have thought possible. Many thanks are also due to Dr. Babak Zamanlooy and Dr. Muhammad Nummer whose knowledge, help and advice I shamelessly exploited.

Special thanks is owed to the remaining members of the Ottawa TSMC mixed-signal design team, including Robert Abbott, Dr. Xin-Jie Wang and Dr. Shahaboddin Moazzeni, for their technical contributions. Additionally, the essential work done by the layout team, Rolando Villanueva and Micheal Kozlov, as well as the test and analysis effort carried out by Tae-Young Goh and Dr. Rolando Ramirez needs to be recognized.

Also, I am very grateful for the generous help given to me by friends and colleagues Jerzy Wieczorkiewicz and Dr. Augusto Lima, as well as the many technical and non-technical discussion with fellow graduate students Xing Zhou and Dr. Nahla AbouElKheir.

Much thanks is owed to the faculty and staff of the Electronics Department of Carleton University for their support throughout my graduate work. Finally, this work would not have been possible without the organizational support I received from TSMC through Cormac O'Connell.

# Table of Contents

| Ał  | ostra         | nct                                   | ii  |

|-----|---------------|---------------------------------------|-----|

| Ac  | kno           | wledgments                            | v   |

| Га  | ble o         | of Contents                           | vi  |

| Lis | st of         | Tables                                | ix  |

| Lis | st of         | Figures                               | xi  |

| No  | omer          | nclature                              | xiv |

| 1   | Int           | roduction                             | 1   |

|     | 1.1           | Motivation                            | 1   |

|     | 1.2           | Objectives, Contributions and Novelty | 7   |

|     | 1.3           | Conference and Journal Submissions    | 8   |

|     | 1.4           | Thesis Outline                        | 9   |

| 2   | Ba            | ckground                              | 11  |

|     | 2.1           | Industry Direction                    | 11  |

|     | 2.2           | FinFET Transistor Overview            | 14  |

|     | 2.3           | SERDES Applications                   | 16  |

|     | 2.4           | Bang Bang Phase Locked Loop (BBPLL)   | 18  |

| 3   | $\mathbf{Th}$ | e Bang Bang Phase Locked Loop         | 22  |

|     | 3.1           | Introduction                          | 22  |

|     | 3.2           | Bang Bang Phase Detector              | 24  |

|     | 3.3           | Digital Loop Filter                   | 30  |

|     | 3.4           | LSB Dithering - Sigma Delta Modulator | 33  |

|   | 3.5  | Linearization of BBPLL Loop Equations                          | 34             |

|---|------|----------------------------------------------------------------|----------------|

|   | 3.6  | Application of Linearized Loop Equations                       | 41             |

|   | 3.7  | Summary                                                        | 44             |

| 4 | The  | e DCO                                                          | 46             |

|   | 4.1  | Introduction                                                   | 46             |

|   | 4.2  | Specification                                                  | 51             |

|   | 4.3  | Varactor Selection                                             | 52             |

|   | 4.4  | Tuning Array Range and Resolution                              | 56             |

|   | 4.5  | $Con/Coff\ Optimization\ .\ .\ .\ .\ .\ .\ .\ .$               | 61             |

|   | 4.6  | Row Loss Minimization - Q Optimization                         | 64             |

|   | 4.7  | Class-C Oscillator Architecture                                | 65             |

|   | 4.8  | DCO Model Simulation                                           | 71             |

|   | 4.9  | DCO Implementation                                             | 79             |

|   | 4.10 | Description of Frequency Tuning Array Rows                     | 84             |

|   | 4.11 | 28-GHz and 14-GHz Inductor Designs                             | 87             |

|   | 4.12 | Summary                                                        | 93             |

| 5 | DC   | O Current Source                                               | 95             |

|   | 5.1  | Introduction                                                   | 95             |

|   | 5.2  | Constant Current Source Implementation                         | 96             |

|   | 5.3  | Thermal and Flicker Noise in FinFET Devices                    | 98             |

|   | 5.4  | Noise Reduction from Source Degeneration                       | 104            |

|   | 5.5  | Summary                                                        | 110            |

| 6 | вв   | PLL Time-Based Simulation and Measurement                      | 112            |

|   | 6.1  | Introduction                                                   | 112            |

|   | 6.2  | The Time-Based Model                                           | 113            |

|   | 6.3  | DCO Noise Model Generation                                     | 113            |

|   | 6.4  | Crystal Oscillator                                             | 118            |

|   | 6.5  | PLL Closed-Loop Noise Prediction                               | 118            |

|   | 6.6  | Summary                                                        | 121            |

|   |      |                                                                |                |

| 7 |      | nulation and Test Results                                      | 122            |

| 7 |      | nulation and Test Results Simulated Results and Die Micrograph | <b>122</b> 122 |

| 7.3     | Phase-Locked Loops in Wireline (SERDES) Applications | 128 |

|---------|------------------------------------------------------|-----|

| 8 Coi   | nclusions and Future Work                            | 131 |

| 8.1     | Conclusions                                          | 131 |

| 8.2     | List of Contributions                                | 132 |

| 8.3     | Future Work                                          | 133 |

| List of | References                                           | 136 |

| Append  | dix A Oscillator Phase Noise                         | 144 |

| Append  | dix B Array Resolution Derivation                    | 156 |

| Append  | dix C DCO Model Code                                 | 159 |

| C.1     | Contents - row_evaluation.m                          | 159 |

| C.2     | Contents - DCO_tuning_range_evaluation.m             | 166 |

| Append  | dix D Inductor Leg Parasitic Analysis                | 171 |

# List of Tables

| 3.1  | BBPLL Loop Parameters for $A_I=1$ and RMS Jitter $\sigma_{\Delta t}=150$ fs    | 43  |

|------|--------------------------------------------------------------------------------|-----|

| 4.1  | Varactor Capacitance/Finger (aF)                                               | 55  |

| 4.2  | Varactor Con/Coff Ratio per Finger (aF/aF)                                     | 55  |

| 4.3  | Varactor Q/Finger                                                              | 56  |

| 4.4  | Type II/III Row Varactor Pair Delta Capacitance                                | 58  |

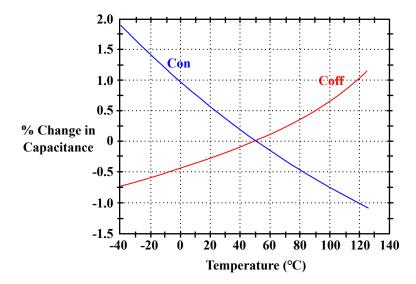

| 4.5  | PVT Variation of Varactor Capacitance                                          | 64  |

| 4.6  | Minimum Q Across Type I Row for A, B, C and D Layouts                          | 64  |

| 4.7  | Min/Max Type I Row Q for A, B, C and D Layouts Across Corners .                | 65  |

| 4.8  | Large Signal Simulation Capacitance Results for Slow/Fast PVT and              |     |

|      | Layout Extraction rcworst_CCworst/rcbesst_CCbest                               | 72  |

| 4.9  | Tuning Range and Loss at 28.0 GHz - Layout A (Slow - reworst CCworst)          | 74  |

| 4.10 | Tuning Range and Loss at 28.0 GHz - Layout B (Slow - reworst CCworst)          | 74  |

| 4.11 | Tuning Range and Loss at 28.0 GHz - Layout C (Slow - reworst CCworst)          | 74  |

| 4.12 | Tuning Range and Loss at 28.0 GHz - Layout D (Slow - reworst CCworst)          | 75  |

| 4.13 | Large Signal Capacitance for Worst, Typical and Best Corners                   | 76  |

| 4.14 | Frequency Control Word (S) Derivation                                          | 81  |

| 4.15 | Skin Depth Comparison and Current Crowding Factor                              | 89  |

| 4.16 | HF Resistance Including Skin Effect and Current Crowding                       | 90  |

| 4.17 | Inductor Field Solver Analysis at 28 GHz                                       | 90  |

| 4.18 | Extracted DC Resistance by Corner                                              | 91  |

| 4.19 | Inductor Field Solver Analysis at 14 GHz                                       | 93  |

| 5.1  | Current Source Degeneration Results for $R_S = 420 \Omega \dots 1$             | 106 |

| 5.2  | Noise Reduction due to Reduced $I_{ds}$ for Values of $R_S$                    | 109 |

| 5.3  | Noise Reduction Factors due to Degeneration for Values of $R_S$                | 110 |

| 5.4  | Calculated Flicker and Thermal Noise Reduction for Values of $\mathcal{R}_S$ 1 | 110 |

| 5.5  | Total Noise Reduction - Simulated vs. Calculated                               | 111 |

| 6.1  | DCO Parameter Values                                                           | 116 |

| 6.2 | DCO Parameter Values                            | 117 |

|-----|-------------------------------------------------|-----|

| 6.3 | Simulated vs. Measured Jitter (1 kHz - 100 MHz) | 119 |

| 7.1 | Simulated Results                               | 122 |

| 7.2 | Contemporary SERDES PLL Performance Comparison  | 130 |

# List of Figures

| 2.1  | Planar MOSFET vs. FinFET Transistors Layout                                                                     | 15 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Cross Section of FinFET Transistors                                                                             | 15 |

| 2.3  | SERDES Application                                                                                              | 17 |

| 2.4  | All Digital Phase Locked Loop with LC-Tank DCO                                                                  | 19 |

| 2.5  | Bang Bang Phase Locked Loop                                                                                     | 21 |

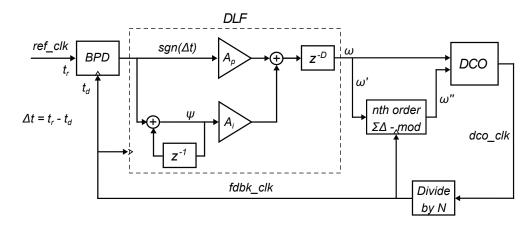

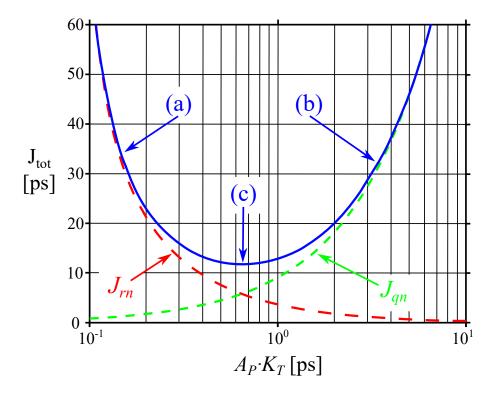

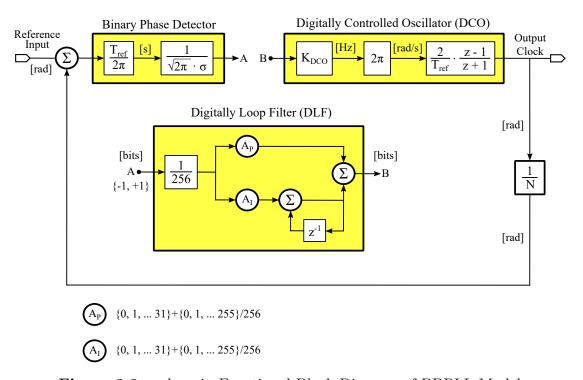

| 3.1  | Second-Order Digital Bang-Bang PLL Functional Block Diagram                                                     | 23 |

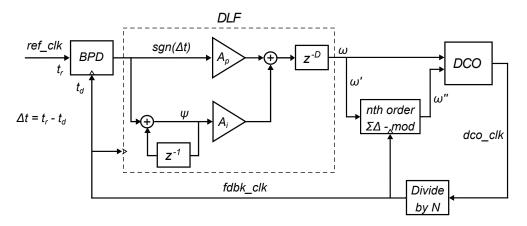

| 3.2  | a), b), c) Gaussian and d), e) f) Uniform Jitter Convolution                                                    | 25 |

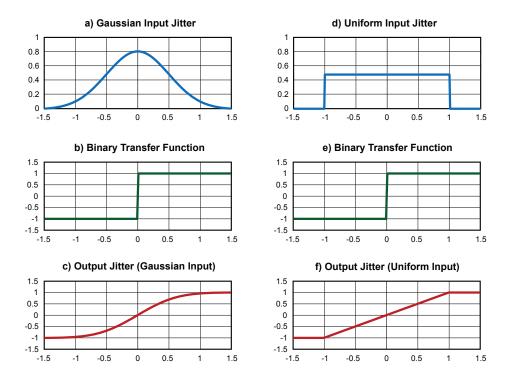

| 3.3  | BBPLL Jitter Component vs. Loop Gain Example                                                                    | 29 |

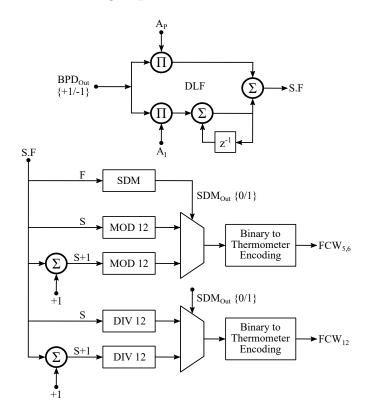

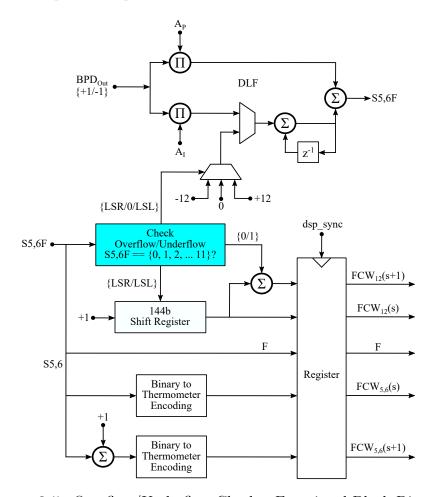

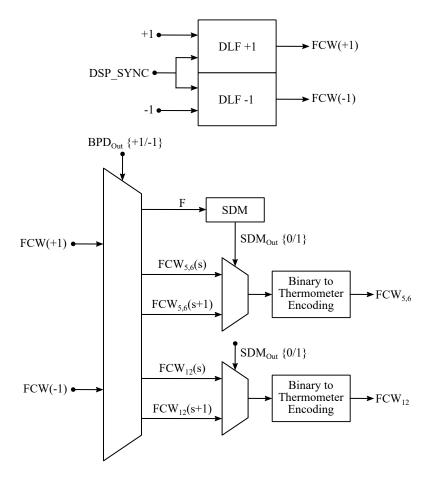

| 3.4  | BPD to DCO Control Path Functional Block Diagram                                                                | 31 |

| 3.5  | Overflow/Underflow Checker Functional Block Diagram                                                             | 32 |

| 3.6  | DLF Look-Ahead Structure Functional Block Diagram                                                               | 33 |

| 3.7  | z-domain BBPLL Model                                                                                            | 35 |

| 3.8  | z-domain Functional Block Diagram of BBPLL Model                                                                | 36 |

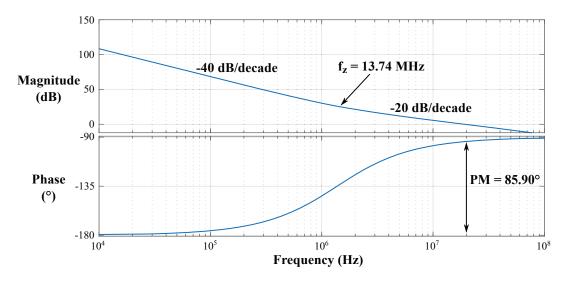

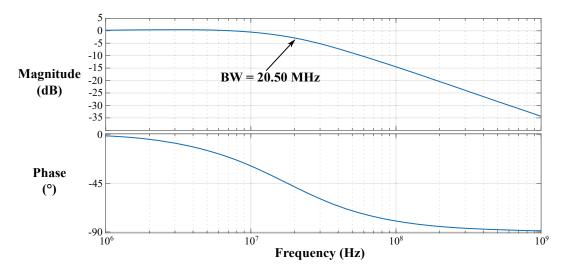

| 3.9  | BBPLL Open Loop Response - $A_P/A_I=40/1,\mathrm{RMS}$ Jitter = 150 fs .                                        | 42 |

| 3.10 | BBPLL Closed Loop Response - $A_P/A_I=40/1, \text{RMS Jitter}=150 \text{ fs}$                                   | 42 |

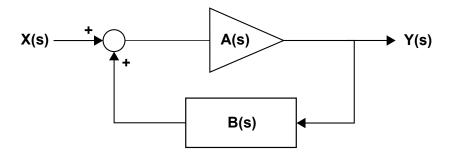

| 4.1  | Classical Linear Feedback Model                                                                                 | 47 |

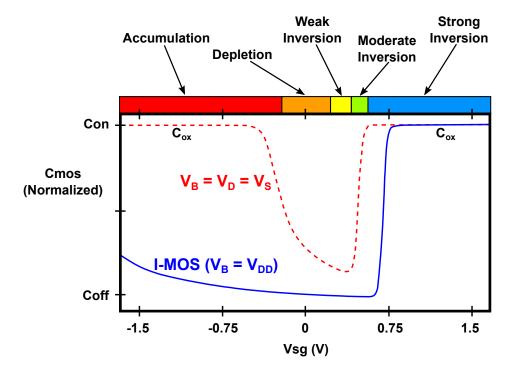

| 4.2  | $\label{eq:comulation-Mode} \mbox{Accumulation-Mode vs. Inversion-Mode PMOS n-Well Varactor} \ \ . \ \ . \ \ .$ | 53 |

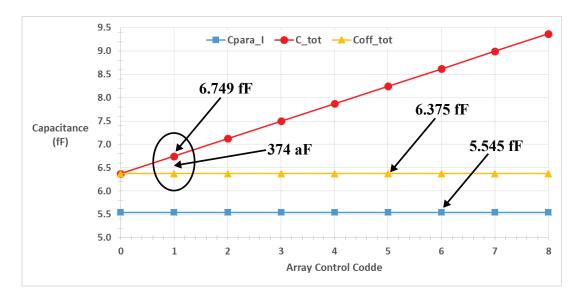

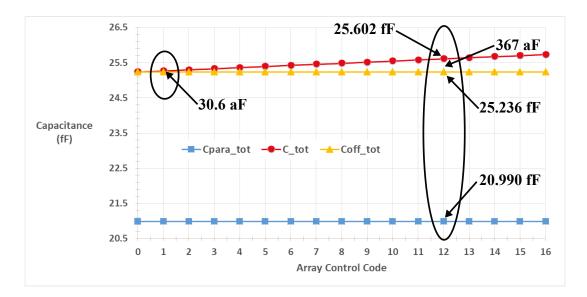

| 4.3  | Row Type II/III $\Delta$ -Capacitor Configuration                                                               | 58 |

| 4.4  | Typical Capacitance - Row Type I                                                                                | 59 |

| 4.5  | Typical $\Delta$ -Capacitance - Row Type II/III                                                                 | 60 |

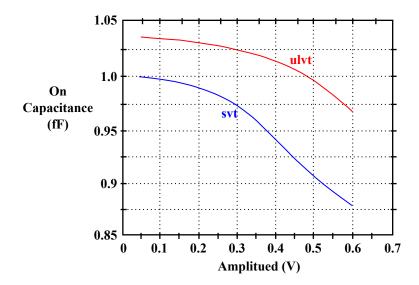

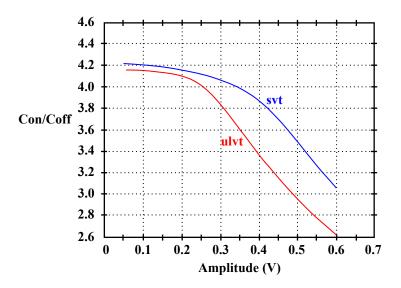

| 4.6  | On Capacitance (6 Fin, L = 36 nm, 1 Finger) svt, ulvt vs. Amplitude                                             | 61 |

| 4.7  | On/Off Capacitance Ratio (6 Fin, $L=36$ nm, 1 Finger) svt, ulvt vs.                                             |    |

|      | Amplitude                                                                                                       | 62 |

| 4.8  | On/Off Capacitance (6 Fin, L = 36 nm, 1 Finger) Temperature Sensi-                                              |    |

|      | tivity                                                                                                          | 63 |

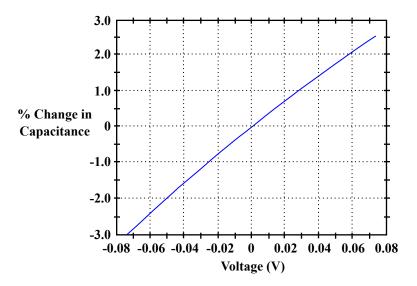

| 4.9  | Varactor (6 Fin, L = 36 nm, 1 Finger) Voltage Sensitivity $\dots$                                               | 63 |

| 4.10 | Class-C Oscillator Core                                                                                         | 67 |

| 4.11 | DCO Normalized Bias Current                                          | 69  |

|------|----------------------------------------------------------------------|-----|

| 4.12 | Class-C Oscillator Biasing                                           | 70  |

| 4.13 | DCO Tuning from Model and Simulation - 28 GHz                        | 77  |

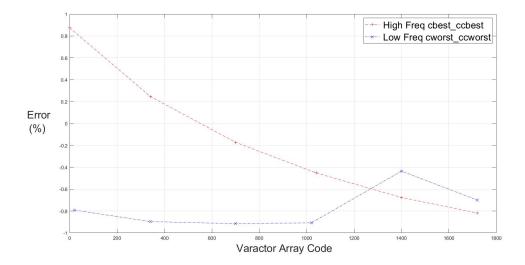

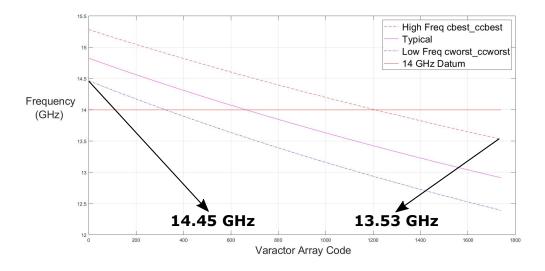

| 4.14 | DCO Tuning Error - Model vs. Circuit Simulation Over Corners         | 78  |

| 4.15 | DCO Tuning from Model and Simulation - 14 GHz                        | 78  |

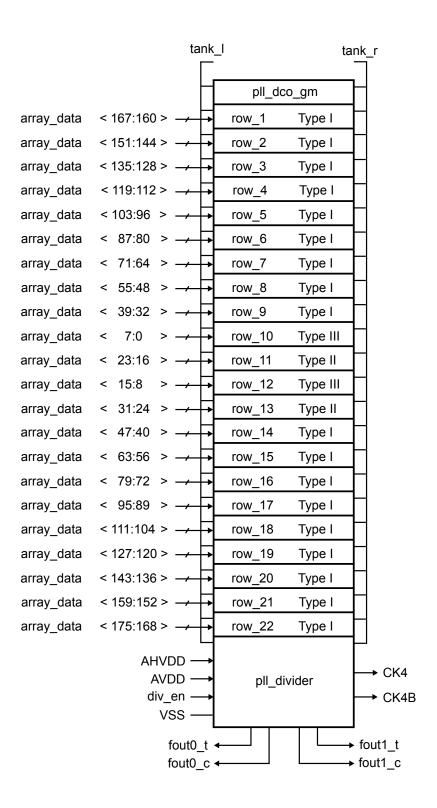

| 4.16 | DCO Core Functional Block Diagram                                    | 80  |

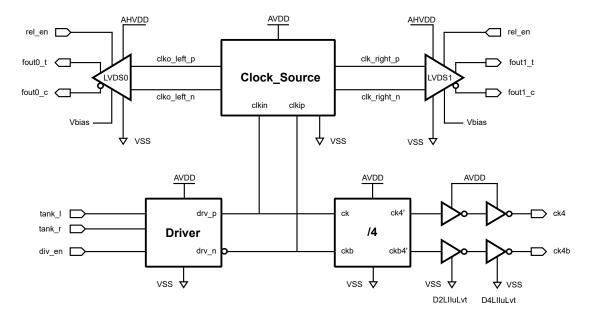

| 4.17 | DCO Clock Buffer and Distribution Functional Block Diagram           | 82  |

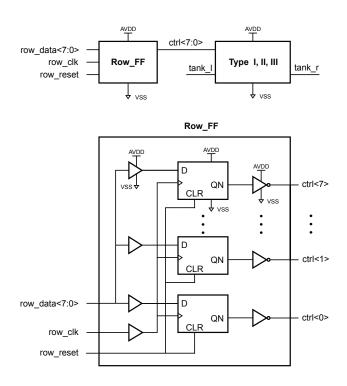

| 4.18 | DCO Varactor Row Control Functional Block Diagram                    | 83  |

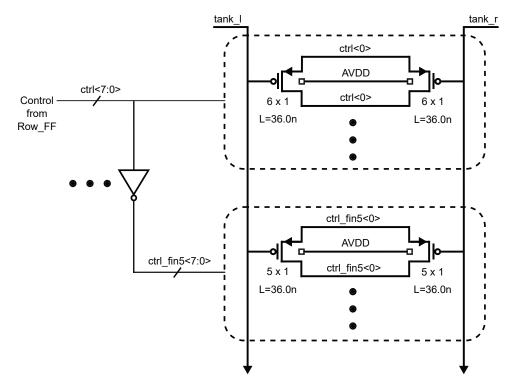

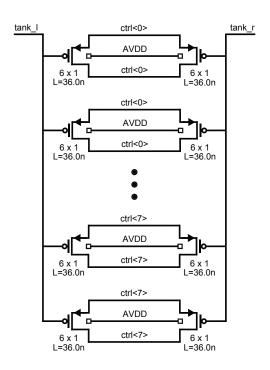

| 4.19 | DCO Type I Varactor Row                                              | 84  |

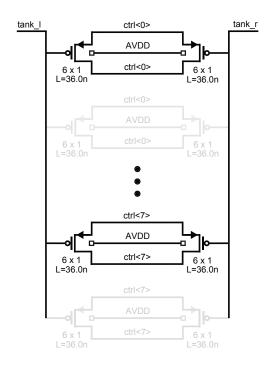

| 4.20 | DCO Type II Varactor Row                                             | 85  |

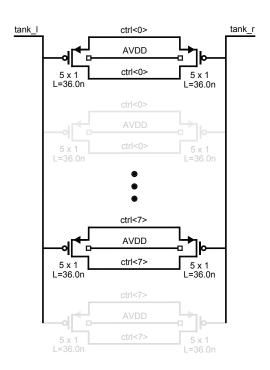

| 4.21 | DCO Type III Varactor Row                                            | 86  |

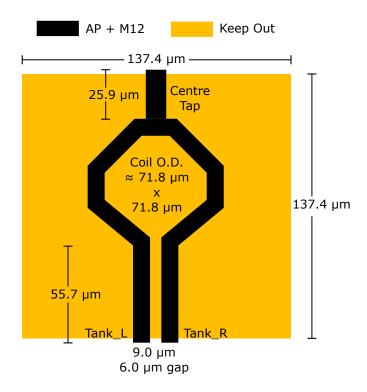

| 4.22 | DCO Inductor Layout for 28.0 GHz Operation                           | 88  |

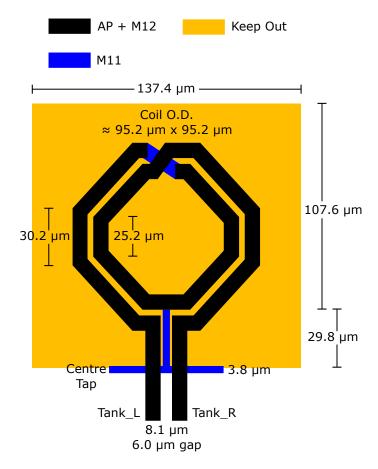

| 4.23 | DCO Inductor Layout for 14 GHz Operation                             | 92  |

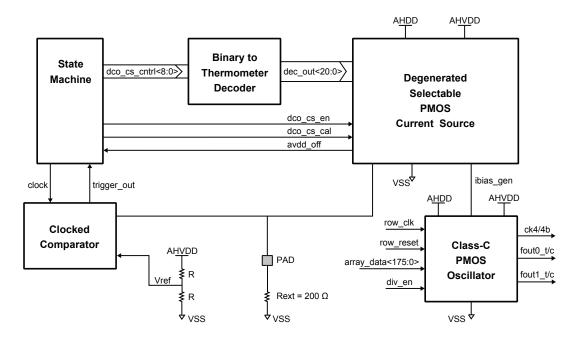

| 5.1  | Oscillator Current Level Calibration Block Diagram                   | 96  |

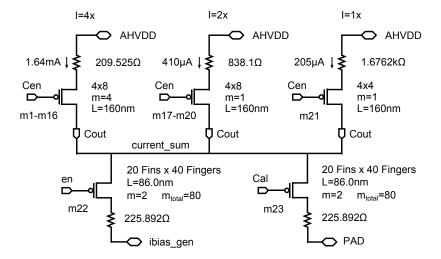

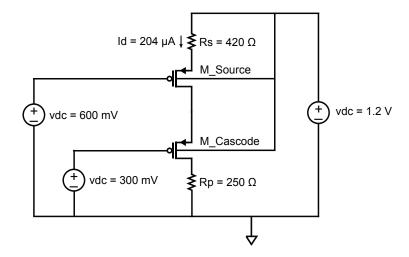

| 5.2  | Degenerated Selectable PMOS Current Source Implementation            | 98  |

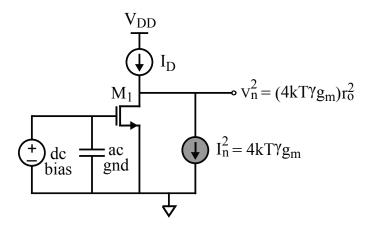

| 5.3  | Channel Noise Circuit                                                | 96  |

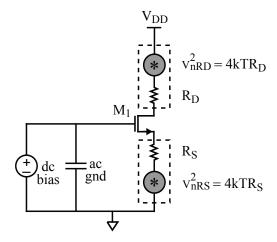

| 5.4  | Source and Drain Interconnect Noise Circuit                          | 100 |

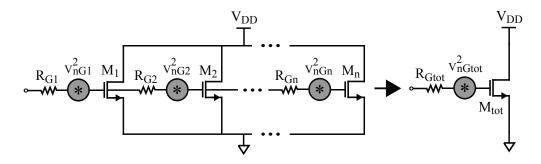

| 5.5  | Gate Interconnect Noise Circuit                                      | 101 |

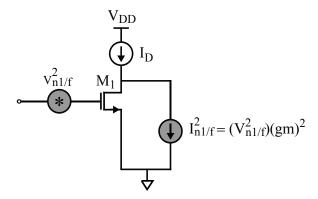

| 5.6  | Flicker $(1/f)$ Noise Circuit                                        | 102 |

| 5.7  | Channel Noise Degeneration Test Circuit                              | 106 |

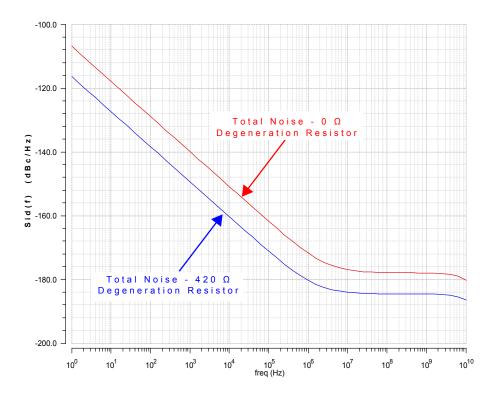

| 5.8  | M_Source $1/f$ and Thermal Phase Noise Before and After Degeneration | 107 |

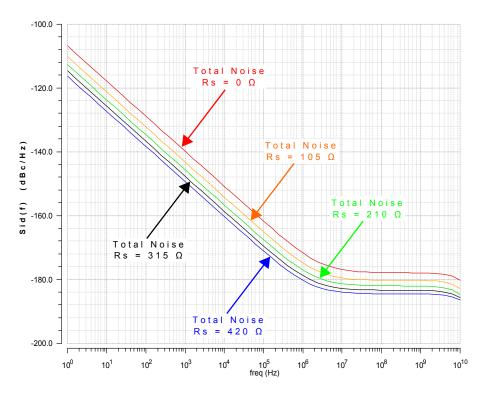

| 5.9  | Total M_Source Noise for Incremental Values of $R_S$                 | 108 |

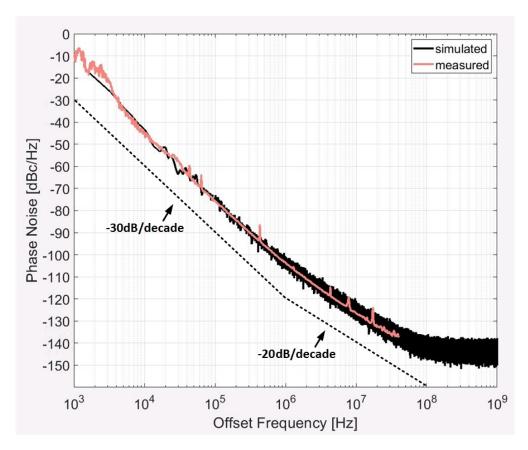

| 6.1  | DCO Phase Noise - Simulated vs. Measured                             | 115 |

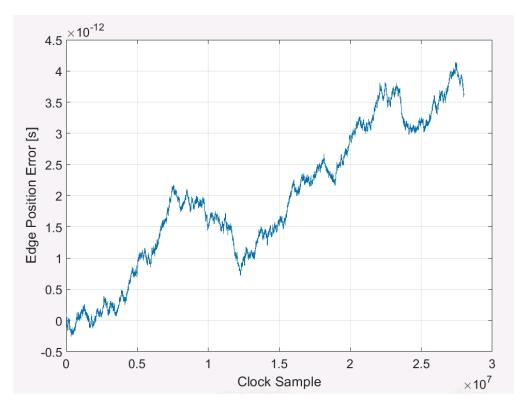

| 6.2  | DCO Edge Position Error with 1-fs Resolution Jitter Calculations     | 117 |

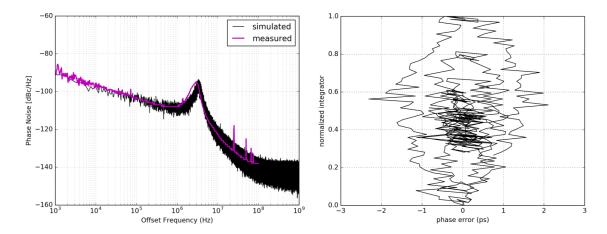

| 6.3  | BBPLL Phase Noise and Trajectory - $A_I = 2, A_P = 7$                | 120 |

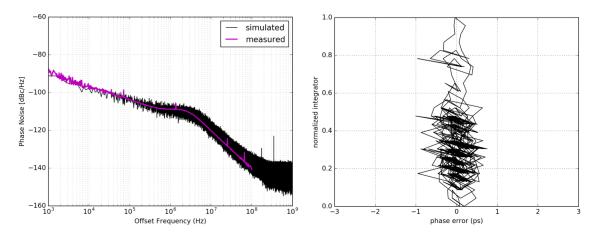

| 6.4  | BBPLL Phase Noise and Trajectory - $A_I = 1, A_P = 40 \dots$         | 120 |

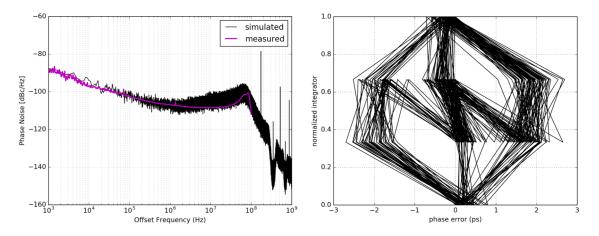

| 6.5  | BBPLL Phase Noise and Trajectory - $A_I=100,A_P=2031$                | 120 |

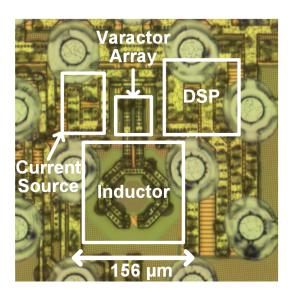

| 7.1  | BBPLL Die Micrograph - 7-nm Process                                  | 123 |

| 7.2  | Measured PN (1 kHz to 100 MHz Offset) - 14-GHz Output Frequency.     | 124 |

| 7.3  | Periodic Jitter Measurement                                          | 125 |

| 7.4  | Breakdown of PN Contributors                                         | 126 |

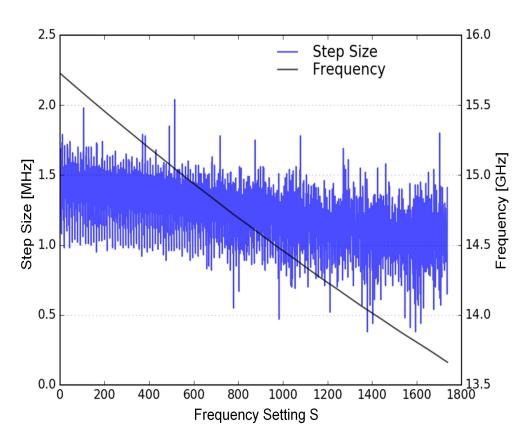

| 7.5  | DCO Frequency Tuning characteristic and Step Size                    | 127 |

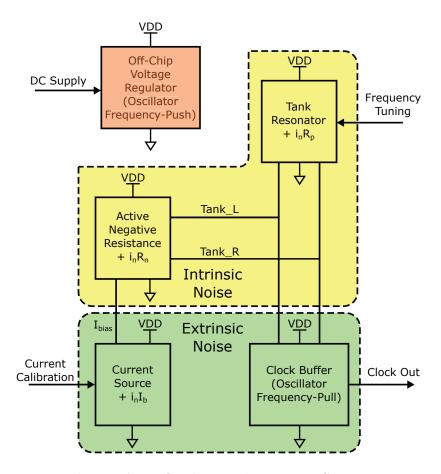

| A.1  | Oscillator Phase Noise Sources                                       | 144 |

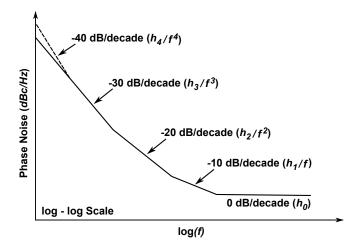

| A 2  | Oscillator Phase Noise Spectrum                                      | 146 |

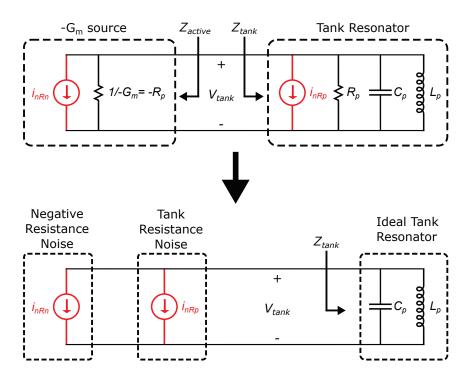

| A.3 | Tank Resonator Intrinsic Noise Sources                            | 147 |

|-----|-------------------------------------------------------------------|-----|

| A.4 | Impulse Sensitivity Function LC vs. Ring Oscillaor                | 151 |

| A.5 | Impulse Sensitivity Function for LC Oscillator                    | 152 |

| A.6 | Noise Conversion from Intrinsic Noise Sources                     | 153 |

| A.7 | Noise Conversion from the Current Source                          | 154 |

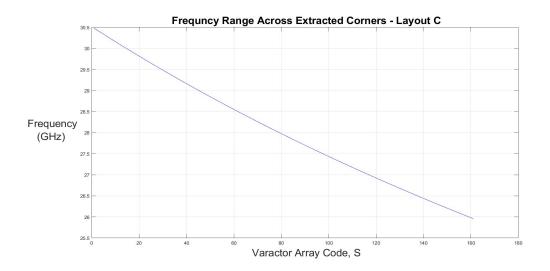

| C.1 | 28-GHz Frequency Tuning Range with 20 Rows                        | 164 |

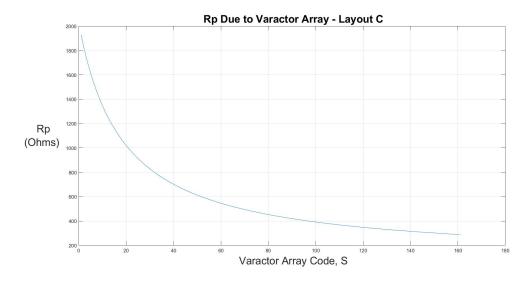

| C.2 | Parallel Array Resistance - 28 GHz                                | 164 |

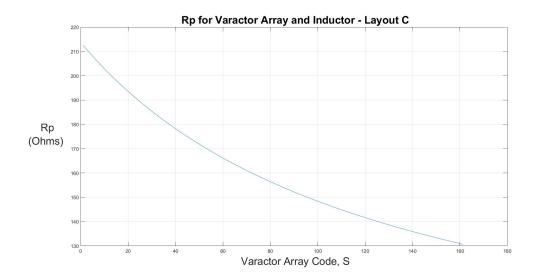

| C.3 | Parallel Resistance Including Inductor and Array - 28 GHz $\cdot$ | 165 |

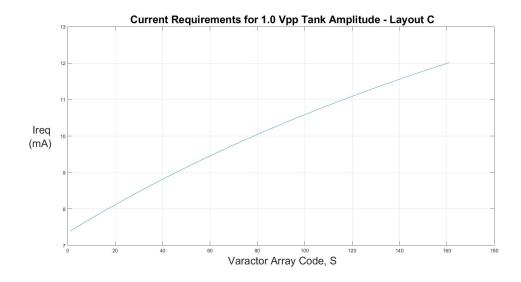

| C.4 | Required DCO Current - 28 GHz                                     | 165 |

| C.5 | Tank Amplitude from 10 mA - 28 GHz                                | 166 |

| D.1 | DCO Leg Inductance                                                | 171 |

# Nomenclature

#### Abbreviations

AC Alternating Current

Accumulation-Mode Biasing of a metal-oxide-silicon semiconductor stack so

majority carriers accumulate in the silicon near the

oxide-silicon interface.

ADPLL All-Digital Phase Locked Loop

aF atto-Farad

AF Flicker noise exponent

AHVDD Analogue High VDD for input/output - nominal 1.5 V.

AHVSS Analogue High VSS for input/output - ground voltage.

AI or  $A_I$  Digital Loop Filter Integral Gain

Al Aluminum

AM Amplitude Modulation

AP (context - interconnect) - metal (Al) layer used to break-

out signals to die bump pads, TSMC 7-nm process

(thickest,  $t = 2.4 \mu m$ ).

AP or  $A_P$  (context - Digital Loop Filter) Proportional gain

AVDD Analogue DC supply voltage (VDD) - core transistor

voltage - nominal 0.75 V.

AVSS Analogue DC ground reference voltage (VSS) - core

transistor voltage.

BBPD Bang-Bang Phase Detector

BBPFD Bang-Bang Phase Frequency Detector

BBPLL Bang-Bang Phase Locked Loop

BER Bit Error Ratio

Biploar Binary Junction Transistor (BJT)

BPD Binary Phase Detector

BSIM4 Berkeley Short Channel (IGFET - Integrated Field Ef-

fect Transistor) Model (4 - sub-100 nm).

BW Bandwidth - contiguous frequency range.

$C_{div}$  Total capacitance of the oscillator output buffer and di-

vider.

$C_{gm}$  Total capacitance of the oscillator core transistors.

CICC Custom Integrated Circuits Conference

Class-A Oscillator A harmonic oscillator where current flows continuously

during the full output clock cycle.

Class-B Oscillator A differential implementation of a Class-A oscillator.

Class-C Oscillator A differential harmonic oscillator having a current con-

duction angle of approximately 100 to 150 degrees.

Class-D Oscillator A differential harmonic switching oscillator that pro-

duces a large output magnitude from a low VDD.

Class-F Oscillator A differential harmonic switching oscillator that employs

transformer peaking to amplify a harmonic output clock.

CMOS Complementary Metal-Oxide Semiconductor

$C_{MOS}$  Capacitance of a Metal-Oxide Semiconductor varactor

Coff Off-state capacitance of a circuit element.

Con On-state capacitance of a circuit element.

$C_{OX}$  MOSFET (FinFET) gate capacitance per unit area  $(F/mum^2)$ .

$C_{para}$  Total parasitic capacitance of the frequency tuning array.

$C_{tail}$  Capacitance between the core transistor common source of a differential oscillator and ground.

Cu Copper

$C_{var}$  Total varactor capacitance of the frequency tuning array.

dB Deci-Bell

dBc Deci-Bell relative to a carrier signal level.

dBc/Hz Deci-Bell relative to a carrier signal level per frequency cycle (Hz).

DC Direct Current

DCC Duty-Cycle Correction

DCD Duty-Cycle Distortion

DCO Digitally Controlled Oscillator

DDR4  $4^{th}$  Generation Double Data Rate Synchronous Dynamic Random-Access Memory (1.2 V, 1600 - 3200 MT/s) defined by JEDEC.

DDR5  $5^{th}$  Generation Double Data Rate Synchronous Dynamic Random-Access Memory (1.1 V, 3200 - 6400 MB/s) defined by JEDEC.

DLF Digital Loop Filter

DLL Delay Locked Loop

EF Flicker noise frequency exponent.

EM 3-D Electromagnetic Three-Dimensional Simulation Tool.

f Frequency (Hz)

FCW Frequency Control Word

FF Fast NMOS/Fast PMOS transistor process corner.

FFT Fast-Fourier Transform

Fin The vertical portion of FinFET gate.

FinFET fin Field-Effect Transistor - fin-shaped gate expanded

into three dimensions.

Finger The physical subdivision of a transistor gate (dimensions

W/L - Width/Length).

Flicker Noise Low frequency phase noise (Pink Noise) having a 1/f

profile at baseband and  $1/f^3$  profile after up-conversion.

Oscillator output frequency (resonant frequency).

fs femto-seconds

GaAs Gallium-Arsenide

Gaussian A statistical distribution generated by data having a

random characteristic.

GIDL Gate-Induced Drain Leakage

gm Transistor conductance measured in Siemens (S).

HF High Frequency

$I_{bias}$  DC Bias current

IC Integrated Circuit

Id Tank\_Left AC drain current through the left core transistor of a

differential oscillator.

Id Tank\_Right AC drain current through the right core transistor of a

differential oscillator.

$I_{ds}$  Transistor drain to source current.

$I_{dso}$  Transistor drain to source current with a source degen-

eration resistance of  $0 \Omega$ .

I-MOS Inversion Mode Metal-Oxide Semiconductor varactor.

$I_n$  Noise current.

$I_{n1/f}^2$  Baseband transistor flicker noise power seen as drain

current.

$I_{nG}^2$  Channel thermal noise current due to gate resistance.

Inversion-Mode Biasing of a metal-oxide-silicon semiconductor stack so

minority carriers accumulate in the silicon near the

oxide-silicon interface.

IO Input/Output

ISF or  $\Gamma$  Impulse Sensitivity Function

$I_{\omega 0}$  Effective oscillator LC-tank current.

Jitter The variation in clock edge position w.r.t. an ideal ref-

erence position.

JSSC Journal of Solid-State Circuits

k (context - noise model generation) clock edge number.

k (context - thermal noise) Boltzmann constant (i.e.,

$1.38064852 \times 10^{-23} \ JK^{-1}$ ).

K AC signal coupling factor across a DC blocking capaci-

tor.

$K_C$  Current crowding factor

KF Flicker noise coefficient

$K_{VCO}$  Voltage Controlled Oscillator conversion gain  $(\Delta f/\Delta V)$ .

L (context - inductor) Inductor or Inductance.

L (context - transistor) gate Length.

$\mathcal{L}(f)$  Single-sided phase noise.

LC Inductor-Capacitor

LC-tank A resonant circuit created using inductor and capacitor

circuit elements.

$L_{eff}$  Effective transistor gate length.

Limit-Cycle Regime PLL operation where output phase/frequency oscillates

about a fixed phase/frequency point.

LMS Least Mean Squares - adaptive filter algorithm that con-

verges to a minimum error.

Loaded-Q The effective Q factor of a circuit, including all parasitic

resistances that would contribute to circuit loss.

LSB Least Significant Bit

LSL Logical Shift Left

LSR Logical Shift Right

LVDS Low-Voltage Differential Signal

m (context - FinFET) transistor multiplier

M11 Metal (Cu) interconnect layer below M12, TSMC 7-nm

process (thickness  $t = 0.72 \ \mu m$ ).

M12 A top layer of metal (Cu) interconnect, TSMC 7-nm

process (thickness  $t = 0.72 \ \mu m$ ).

MCM Multi-Chip Modules

MIM Metal-Insulator-Metal IC capacitor formed using metal

plates of two or more layers requiring additional process

steps.

MOM Metal-Oxide-Metal IC capacitor constructed using mul-

tiple inter-digitated fingers over a single or multiple

metal layers.

MOSFET Metal-Oxide Silicon Field-Effect Transistor

nm nano-meter

$N_{FV}$  Transistor flicker noise voltage in linear form.

NMOS N-type Metal Oxide Semiconductor.

NRZ Non-Return to Zero data encoding for transmission.

$N_{TV}$  Transistor thermal noise voltage in linear form.

P FinFET fin Pitch

PAM-4 Pulse Amplitude Modulation (4-state) data encoding for

transmission.

PDF Probability Density Function

PFD Phase Frequency Detector

PI A circuit with both Proportional and Integral functions.

PISO Parallel In Serial Out

PLL Phase Locked Loop

PM Phase Margin

PM Phase Modulation

PMOS P-type Metal Oxide Semiconductor.

PN Phase Noise

pp peak-to-peak

PSD Power Spectral Density

PSRR Power Supply Rejection Ratio

PSS Periodic Steady State

PVT Process, Voltage and Temperature.

Q Resonator Quality Factor.

$Q_{C\_worst}$  Worst case (PVT and extracted layout) Q of the DCO

tuning array total capacitance.

QEC Quadrature-Error Correction

QED Quadrature-Error Detection

$Q_{DCO\_worst}$  Worst case (PVT and extracted layout) Q of the DCO

tuning array total capacitance plus inductor.

Quantization A process of resolution to a finite number of levels.

rad Radians

rad<sup>2</sup>/Hz Phase noise power spectral density measured in radians

squared per Hz.

rcbest-CCbest Extracted layout parasitic component modelling ex-

hibiting lowest Resistance and Capacitance.

rcworst-CCworst Extracted layout parasitic component modelling ex-

hibiting highest Resistance and Capacitance.

$R_D$  Transistor drain resistance (intrinsic, extrinsic and in-

terconnect).

$R_{DC}$  Resistance at zero frequency.

$R_G$  Transistor gate resistance (intrinsic, extrinsic and inter-

connect).

$R_{HF}$  High-Frequency Resistance.

$R_{lumped}$  Total resistive losses in the metal interconnect between

oscillator varactor array and inductor.

RMS Root Mean Square

$r_o$  Transistor intrinsic resistance.

RO Ring Oscillator

$R_O$  Load Resistance.

$Row\_FF$  Frequency array row D flip-flop.

Rp or  $R_p$  Parallel resistance of a resonator.

$R_{p\_HF}$  Resistance at zero frequency.

Rs or  $R_s$  Series resistance of a resonator.

$R_S$  Transistor source resistance (intrinsic, extrinsic and in-

terconnect).

$R_{s\_DC}$  High-Frequency Resistance.

$R_{s.HF}$  Resistance at zero frequency.

RTL Register Transfer Language

Run-Time The total duration a central processing unit is egaged in

a process from beginning to end result.

s seconds

S (context - FinFET) - subthreshold swing - the gate volt-

age range between drain current on and off-states.

S (context - frequency array) - a set of cardinal numbers

representing the unique states of a frequency tuning ar-

ray.

$S_{noise}(\Delta f)$  Noise power spectral density at frequency offset  $\Delta f$ .

SPD Sampling Phase Detector

SDM Sigma-Delta Modulator

SERDES Serializer/Deserializaer

Si Silicon

$S_{id}(f)$  Noise power spectral density

SiGe Silicon-Germanium

Signum Sgn function - input quantized to output value -1, 0 or

+1.

SiO<sub>2</sub> Silicon Dioxide

SIPO Serial In Parallel Out

SNR Signal-to-Noise Ratio

SS Slow NMOS/Slow PMOS transistor process corner.

SST Source-Series Transmitter

svt standard voltage threshold

t Thickness of a semiconductor material or metal layer.

T Absolute Temperature ( ${}^{\circ}K$ )

$t_A t_{SU} + t_H = t_A$

tank\_l/L Tank Left - the signal conductor laid out on the left side

of the LC-tank.

tank\_r/R Tank Right - the signal conductor laid out on the right

side of the LC-tank.

TDC Time-to-Digital Converter

TDM Time Division Multiplexing

$t_H$  Hold Time

Thermal Noise Random phase noise directly proportional to heat.

$T_{OX}$  Oxide thickness (nm)

TSMC Taiwan Semiconductor Manufacturing Company

$t_{SU}$  Setup Time

ulsvt Ultra-low voltage threshold

V Volts

Varactor A transistor or diode circuit element used as a capacitor.

$V_B$  Transistor Bulk Voltage

$V_{BG}$  Voltage from transistor bulk to gate.

$V_{bias}$  DC Bias Voltage (also  $V_{bias\_L}$  and  $V_{bias\_R}$ .)

VCO Voltage-Controlled Oscillator

$V_D$  Transistor Drain Voltage

$V_{DD}$  CMOS supply voltage

Vds Voltage from transistor drain to source.

$V_{eff}$  Transistor effective (overdrive) voltage ( $V_{eff} = V_{gs}$  –

$V_{th}$ ).

Vgate\_Left Feedback voltage applied to the left differential oscillator

core transistor.

Vgate\_Right Feedback voltage applied to the right differential oscil-

lator core transistor.

Vgd Voltage from transistor gate to drain.

Vgs Voltage from transistor gate to source.

Vm Voltage magnitude

$V_n$  Noise voltage

$V_{n1/f}^2$  Baseband transistor input referred flicker noise power

seen at the gate.

$V_{nG}^2$  Channel thermal noise voltage due to gate resistance.

Vp Peak Voltage

$V_S$  Transistor Source Voltage

Vsg Voltage from transistor source to gate.

Vsource Voltage on the common source of the core transistors of

the differential oscillator.

$V_{SS}$  CMOS supply voltage ground reference.

$\mathbf{V}_T$  or  $\mathbf{V}_{th}$  Transistor Threshold Voltage

$V_{tank_L}$  Voltage on LC-tank conductor tank\_L.

$V_{tank_R}$  Voltage on LC-tank conductor tank\_R.

W Transistor gate Width.

w Width of a semiconductor material or metal layer.

w/t Ratio of width to thickness of a semiconductor material

or metal layer.

Wander Jitter operating below 10 Hz (Red Noise).

$W_{eff}$  Effective transistor gate width.

XO Discrete Crystal Oscillator.

Zeta  $(\zeta)$  Damping Factor.

# **Symbols**

$\gamma$  Transistor coefficient (i.e., short channel devices  $\gamma =$

1.0).

$\delta$  Skin Depth.

$\Delta f_{1/f^3}$  Up-converted flicker-noise corner frequency.

$\zeta$  (zeta) Damping Factor.

$\epsilon_0$  Absolute permittivity (8.854 x  $10^{-12}$  F/m).

$\epsilon_r$  Relative permittivity of silicon ( $\approx 3.9$ ).

$\epsilon_{OX}$  Oxide permittivity ( $\approx 3.9 \times 8.854 \times 10^{-12} \text{ F/m}$ ).

$\mu_0$  Free space vacuum permeability (H/m).

$\mu_r$  Relative Permeability.

$\sigma$  Conductivity (S/m).

$\Sigma\Delta$ -modulator SDM - sigma-delta modulator.

$\omega$  Angular frequency = 2 x  $\pi$  x frequency (radians/s).

$\Omega/\square$  Ohms/square - Resistance ( $\Omega) = \Omega/\square$ x Length/Width.

## Chapter 1

### Introduction

#### 1.1 Motivation

The 7-nm FinFET process, used in this work, was created by TSMC with the objectives of increasing circuit function integration, speed and reducing power dissipation. This process geometry is very expensive, so it can only be used for high volume commercial applications such as cell phones, laptop computers and other portable devices, as well as high data rate network equipment. At this level of integration multiple processor and DSP (Digital Signal Processing) cores, RAM memory blocks, as well as radio and I/O blocks associated with an application are fabricated on the same die. Therefore, high-speed data must be transported across the die without going through I/O structures that would limit data rates, consume valuable pin count and increase power dissipation. This is commonly achieved using SERDES circuit blocks that drive transmission lines implemented using top metal layers. The ultimate goal of the overall project, of which this BBPLL is a critical part, is to implement a SERDES circuit function that will transport data between two circuit blocks on a the same 7-nm die. Therefore, all circuit blocks, including the BBPLL, must be implemented on the 7nm die, except for the BBPLL reference clock, which must originate from an external Crystal Oscillator (XO) [1,2] for performance reasons (i.e., stability and phase noise). The SERDES transmit encoding of four level Pulse-Amplitude Modulation (PAM-4) and a data rate of 56-Gb/s were chosen for this project as they are current industry standard [3].

The goal of this thesis is to reduce the size, power dissipation and output jitter of the high-frequency SERDES clock source by implementing it as an All-Digital Phased-Locked Loop (ADPLL). The following list articulates the major challenges that were overcome to during this development, and also substantiates many of the design decisions.

- 1. DCO type based on the objectives described previously, the ideal DCO would be a ring oscillator implemented using digital library inverter elements. However, as low-jitter (phase noise) was of primary importance for this design, an LC-tank oscillator was chosen. That is, the theoretical maximum Q of a ring oscillator is approximately 1.57, while the loaded-Q of an LC-tank oscillator implemented as an integrated circuit can be in the range of 10 30. Oscillator Q has a squared relationship with phase noise as shown by Leeson (A.20) [4]. See section 2.4 and Appendix A for details.

- 2. LC-tank inductor implementation inductors can be relatively large structures with windings that require a large enough conductive cross-section to minimize losses and maximize Q. It was found that combining the top two metal layers provided adequate metal thickness to support sufficient inductor Q. Additionally, at 28 GHz and 14 GHz the inductor areas were small enough to consider the LC-tank oscillator a reasonable option. See sections 4.2 and 4.11, and Figures 4.22 and 4.23.

- 3. DCO frequency selection with the SERDES transmit data rate of 56 Gb/s, 28 GHz was selected initially as the oscillator resonant frequency. Both the rising and falling clock edges would be used to clock NRZ data (i.e., one bit/symbol, two states/symbol). This clock must be distributed to five transceivers and further distributed within the transceivers using digital library inverter elements. Unfortunately, the gain of these library inverter elements was insufficient for this purpose. In order to overcome this challenge, the original oscillator resonant frequency of 28 GHz was reduced to 14 GHz, reducing the inverter gain requirement. This was achieved by adding a turn to the existing inductor, sufficiently increasing its inductance within the existing footprint. The transmit modulation had to change to PAM-4 (i.e., two bits/symbol, four states/symbol) to accommodate the new transmit clock rate. See sections 4.2 and 4.11 for details.

- 4. Oscillator 7-nm FinFET flicker noise as IC geometry shrinks, flicker noise increases. Although this analysis was considered to be beyond the scope of this

project, it was understood that the baseband flicker noise corner of this 7-nm process could be in the tens or even hundreds of MHz, depending on transistor size. The following measures were taken to mitigate this issue:

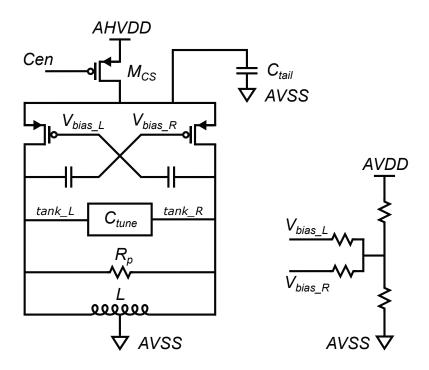

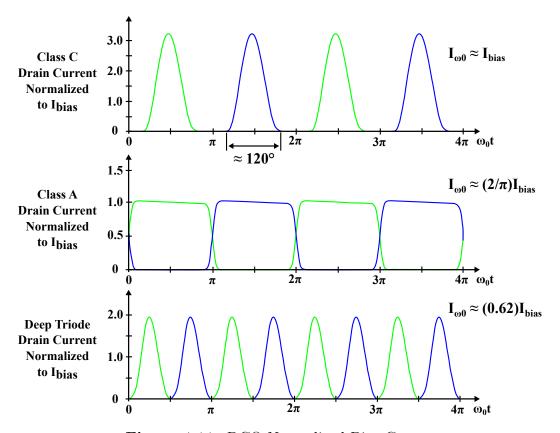

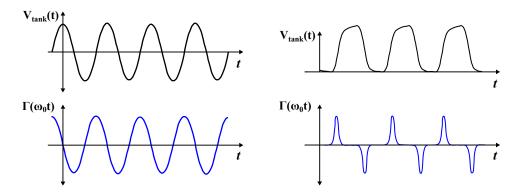

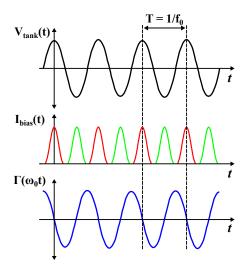

- (a) A class-C oscillator architecture [5] was selected based largely on its reduced conduction angle. That is, phase noise from the current source and core transistors is present in the oscillator during the period (i.e., conduction angle) when current is injected into the LC-tank. Reducing the conduction angle from 180° for a conventional oscillator to ≈ 120° for class-C reduces this noisy period. See section 4.7 and Figure 4.11 for details. It should be noted that the class-C oscillator current conduction angle is larger than the typical class-C power amplifier conduction angle (i.e., 90°). This is due to the stability requirements of the oscillator, which unlike a power amplifier, requires positive feedback to sustain oscillation see squegging and Figures 10 to 12 in [5].

- (b) The class-C oscillator architecture requires a large bypass capacitor connected from the common source node of the core transistors to ground. This not only supports class-C operation, but provides a low impedance path for noise to ground. See section 4.7 and Figure 4.10 for details.

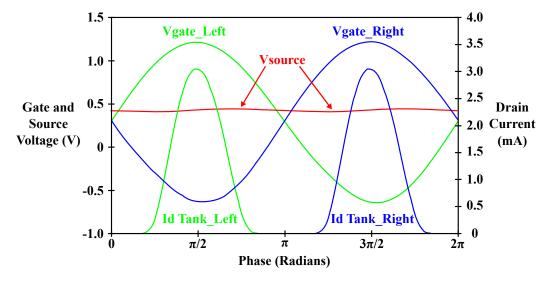

- (c) Oscillator core transistor gate bias was selected to maximize the output amplitude. This maximizes the signal to noise ratio of the output. Care must be taken to ensure that the transistor breakdown voltage limit is never exceeded. See section 4.7 and Figure 4.12 for details.

- (d) The size of the DC-blocking capacitors used to isolate the gate bias voltage on the oscillator core transistors was carefully selected to minimize distortion of the oscillator feedback signal. This minimizes the amount of flicker noise that is up-converted from baseband to skirt the oscillator output frequency. See section 4.7 and Figure 4.10 for details.

- (e) A method of oscillator current source calibration was implemented to ensure maximum oscillator output amplitude (i.e., maximum SNR) across PVT variations. See section 5.2 and Figure 5.1 for details.

- (f) Source-degeneration of the current source transistors was used to reduce baseband flicker and thermal noise that is up-converted into the channel of oscillator core transistors. The degenerated current source transistors

form a cascode transistor pair with the core transistors. Therefore, the noise current in the core transistors is not significant as it is limited by the current source transistors. See section 5.4, Figure 5.7 and (5.19) for details.

- (g) Design priority was given to reducing loss and improving the Q of the LC-tank (Varactor array row loss see section 4.6 and inductor loss see section 4.11, as well as section 4.8).

- 5. Oscillator core layout oscillator core transistor layout was carefully interdigitated to minimize core transistors element interconnect losses and ensure current density requirements were met. Both these measures were necessary to guarantee the oscillator core produced enough gain and current to oscillate at frequency without exceeding thermal requirements. It should be noted that the M0 layer interconnect models were revised periodically during this design work.

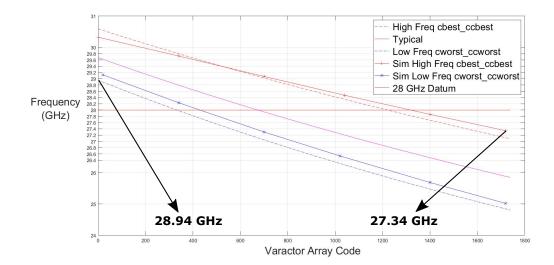

- 6. DCO array tuning range the size and architecture of the DCO frequency tuning array needed to be determined and verified to be adequate to compensate of PVT and layout variation extremes. This was achieved by creating a MATLAB® model of the DCO, which allowed accurate and timely testing of various array designs. See section 4.8 and Appendix C for details.

- 7. DCO varactor design for range FinFET varactor element sizing was optimized for maximize Con/Coff ratio and Q, as well as minimum array physical size and tuning resolution. This was achieved using both small-signal and large-signal simulation. Additionally, care was taken to ensure these devices were large enough to mitigate element matching issues. See sections 4.3, 4.4 and 4.5 for details.

- 8. DCO varactor design for resolution DCO tuning array resolution was maximized by optimizing the fine tuning varactor elements to minimize Con/Off ratio, while maintaining Q. The difference or  $\Delta$ -capacitance between two larger varactor elements was used here to ensure frequency tuning curve monotonicity (i.e., adequate element matching). See sections 4.3, 4.4 and 4.5 for details.

- 9. Phase detector selection conventional ADPLL designs use a Time-to-Digital Converter (DTC) as a phase-frequency detector. This represents considerable

- design effort that results is a relative large circuit requiring significant current. Its resolution is limited by the semiconductor process and is susceptible to PVT variations. These issues were mitigated by replacing the TDC with a Binary Phase Detector (BPD), implemented as a D flip-flop. See section 3.2 for details.

- 10. Quantization noise BBPLL DCO frequency tuning is not continuous and the BPD produces a scalar phase error. These two circuit functions combine to generate quantization noise that is not present in an analogue PLL with continuous VCO tuning. Therefore, while an ADPLL does not have as many sources of large thermal noise (e.g., loop filter resistors, charge pump ...) it contributes quantization noise and associated frequency spurs. However, the DCO thermal noise can be used to randomize the quantization noise and spread it and its frequency spurs across the frequency spectrum noise floor. See sections 3.1 and 3.2 for details.

- 11. BBPLL analysis the nonlinearity of the Binary Phase Detector (BPD) used by the BBPLL makes loop analysis for stability, phase margin and phase noise difficult. Analysis employing bilinear transforms was carried out and yielded competent, but optimistic results See sections 3.5 and 3.6 for details. A verilog model of the DCO was created from the MATLAB® work discussed in item 6 of this list to complete a time-domain model of the full BBPLL. This generated functionally accurate and time-efficient event-driven behavioural simulation results. However, this initial verilog model did not include phase noise from thermal sources (i.e., DCO and XO). See sections 6.1 and 6.2 for details.

- 12. Full event-driven BBPLL model a complete model of the BBPLL must include phase noise from thermal sources as it affects both jitter performance and loop functionality. This was accomplished by using curve fitting to model the phase noise profiles of the DCO and external XO. These frequency-domain profiles were converted to time-domain jitter vectors containing clock edge variations. A novel approach was used to include these clock edge variations in the event-driven simulation. See sections 6.3, 6.4 and 6.5 for details.

- 13. DLF gain range and resolution the jitter performance of the BBPLL is dependent on a balance between two extreme modes of operation (i.e., limit –

cycle regieme and random - noise regieme). These modes of operation are controlled by the Digital Loop Filter (DLF) gain. Therefore, adequate DLF proportional and integral gain range and resolution must be implemented. See sections 3.2 and 3.3 for details.

- 14. Pre-production 7-nm process during this design the 7-nm FinFET process was in its last stages of development (i.e., pre-production); therefore, circuit elements models were periodically updated. Additionally, some parameters, i.e., FinFET channel loss, were underestimated. In order to overcome these challenges simulations had to be rerun after new model releases and any resulting problems and inaccuracies had to be accounted for in the design.

- 15. Security restrictions Although not a development issue, these restrictions were the most significant barrier to the complete this thesis. TSMC security restrictions are tight. It is absolutely forbidden to record or transport any information or data created inside the TSMC lab to an external environment. This is a well justified policy that is based on specific cases that range from inadvertent disclosure in a PhD thesis to outright industrial espionage. In order to write this thesis all data, circuit diagrams and code had to be recorded by hand and then reproduced for this thesis document. Therefore, actual plots, circuit and layout diagrams, as well as original test data was not available. The test results included in this thesis have been reproduced from the published papers associated with this work.

Validation of the physics and process fabrication, as well as the component models, parasitic models and libraries is fundamental to bringing a new semiconductor process to production. However, despite this work complex circuit implementations using new processes have been known to fail to yield adequately. It needs to be demonstrated that challenges such as high loss of fine interconnect required by the process geometry can be overcome. At the same time, a process scaled and optimized for digital design must also not only support analogue and RF circuits, but be used as a platform for novelty and cutting-edge innovation.

The implementation of a 56 Gb/s SERDES device was selected as an industryrelevant application to demonstrate the capabilities of the TSMC 7-nm FinFET technology, not yet in full production. The company's motivation in doing this project was to show potential customers that complex mixed-signal circuit design in this new process with new circuit models was not only possible, but that it was capable of high yield, and therefore, a low risk undertaking.

While bang-bang PLLs have been ignored previously for low-jitter high-data rate transceivers, recent development work has showed some promise for this type of clock source. Therefore, realization of a BBPLL with state-of-the-art performance was considered an excellent candidate for this design effort.

# 1.2 Objectives, Contributions and Novelty

The objective of this work is to implement a low jitter (low PN with minimal spurs) 14.0-GHz Integer-N BBPLL and clock distribution for a five lane 56-Gb/s PAM-4 SERDES transmitter in TSMC's new 7-nm FinFET technology - see Figure 2.3. The BBPLL DCO is realized as a Class-C LC-tank oscillator [5] tuned using p-type FinFET transistors configured as inversion-mode varactors. FinFET transistors and fine pitch interconnect, targeted for aggressive geometry digital design, will be shown to be capable of attaining state-of-the-art analogue circuit performance. This is achieved by overcoming issues of high interconnect losses, gate resistance, flicker noise and low VDD levels.

The work described in this proposal makes the following contributions to the current state-of-the-art.

- 1. Single-fin modularity is used to implement a fine resolution  $\Delta$ -capacitance of 75 aF. This is made possible as the on-state capacitance of the FinFET PMOS inversion-mode varactors has a linear relationship with the number of fins.

- 2. A new closed form solution quantifying how source degeneration can be used to reduce transistor flicker noise in oscillators is derived. This is important in this application as the flicker noise produced by small geometry transistors is significantly worse than the flicker noise of larger geometry planar MOSFET transistors.

- 3. Taking advantage of the improved performance of the 7-nm process, the digital loop filter in the forward path of the BBPLL is clocked at 10 times the reference frequency and incorporates a lookahead architecture. This new architecture reduces delay or loop latency, which deteriorates jitter performance and phase

margin, that would normally be present if the digital loop filter were clocked at the reference frequency.

- 4. A new method of efficiently incorporating reference oscillator and DCO jitter with digital time-domain event-driven simulation (i.e., verilog simulator) is proposed. This enables full functional and phase noise simulation of the BBPLL, while greatly reducing simulation run-time.

- 5. Digital time-domain simulator run-time is further reduced (by five times) and output jitter error is improved (< 1 % for a 1 ms simulation time) by calculating jitter time-stamp vectors prior to simulation rather than during simulation.

- 6. A novel approach to Large-signal circuit and 3-D EM analyses is proposed to characterize circuit elements and modules to create a mathematical model of the DCO. The run-time of the mathematical model is significantly shorter than that of the DCO circuit simulation, while maintaining accuracy to within  $\pm$  0.9 %. The shortened run-time allows various DCO array architectures and implementations to be optimized quickly and accurately.

This project includes the first design and implementation of an LC-tank Class-C oscillator in TSMC's 7-nm CMOS FinFET process. The success of this implementation demonstrates that this process, optimized for digital design, can also be used to realize analogue circuits exhibiting start-of-the-art performance.

## 1.3 Conference and Journal Submissions

The following two papers have been published as a result of the work described in this proposal. The Custom Integrated Circuits Conference (CICC) paper was selected as one of the top papers of the 2019 Austin, TX Conference. This resulted in an invitation to submit the expanded journal paper listed below, which was included in the March 2020 Journal of Solid-State Circuits (JSSC) special issue.

D. Pfaff, R.Abbott, X.-J. Wang, B. Zamanlooy, S. Moazzemi, R. Smith, C.-C. Lin, "A 14-GHz Bang-Bang Digital PLL with sub-156fs Integrated Jitter for Wireline Applications in 7nm FinFET," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Austin, TX, USA, Apr. 2019, pp. 1-4.

2. D. Pfaff, R. Abbott, X.-J. Wang, S. Moazzemi, R. Mason, R.R. Smith, "A 14-GHz bang-bang digital PLL with sub-156fs integrated jitter for wireline applications in 7nm FinFET CMOS," IEEE J. Solid-State Circuits (JSSC), vol. 55, no. 3, Mar. 2020, pp. 580-591.

The order of the list of authors' names for the above papers is TSMC followed by Carleton University as required by TSMC. The author of this thesis was the main author of these papers and the major contributor to the development of the BBPLL discussed in these papers.

#### 1.4 Thesis Outline

Chapter 2 establishes the background necessary to understand the motivation and objectives of the remaining chapters of this thesis. It briefly discusses four topics ranging from the forces governing the direction of the industry and this project, the motivation for FinFET transistor technology, the application of SERDES interfaces, as well as a general description of Bang Bang Phase Locked Loop (BBPLL) devices.

Chapter 3 presents the requirements, architecture, concepts and design of the SERDES Bang Bang PLL. Linear loop equations are derived and used to approximate bandwidth and stability.

Chapter 4 explains the DCO architecture selection and implemented. Issues such varactor configuration and capacitance resolution; loss minimization (i.e., Q maximization) for various varactor row layouts, frequency range over PVT and extracted corners versus the number of varactor rows; and Inductor design and layout. A novel method of accurately plotting frequency versus tuning-array setting that includes loss, parasitic capacitance, as well as linear and non-linear varactor capacitance is demonstrated.

Chapter 5 discusses the DCO current source design and techniques used to reduce DCO noise. A closed form equation is derived for source degeneration flicker noise reduction.

In Chapter 6 transient simulation of the BBPLL in the time domain is discussed in detail. Also, a novel method of jitter (phase noise) analysis is demonstrated.

Chapter 7 discusses the simulated and measured results, and presents a die micrograph of the BBPLL implemented in 7-nm CMOS FinFET technology.

Chapter 8 presents the conclusions and proposes areas of future work. A list of contributions, as well as conference and journal publications are also included.

Appendix A articulates some fundamental oscillator and oscillator noise concepts that apply directly the class-C [5] DCO demonstrated in this work. Appendix B presents the derivation of an equation for frequency tuning array step size resulting from a corresponding capacitance step. This is consistent with [6]. Appendix C is the MATLAB® code used to model the DCO frequency tuning array discussed in section 4.8. Appendix D is an analysis of the inductor leg interconnect parasitics.

### Chapter 2

# Background

### 2.1 Industry Direction

Classical phase locked loop design has been largely an analogue-domain undertaking with only a few digital components to implement the feedback divider and phase-frequency detector. Analogue loop filters needed to be constructed using external discrete elements (i.e., capacitor, resistors, Op-Amps ...) to realize the required loop bandwidth and stability. Voltage controlled oscillators have taken forms such as relaxation, ring, LC-tank harmonic, pulled quartz crystal, rotary travelling wave, as well as transmission line, ceramic piezoelectric and surface acoustic wave resonators [7]. These phase locked loop implementations served the industry well as they could be reliably produced at low cost to yield consistent performance. However, they suffer form large parasitics that limit their frequency of operation, large physical size that limits the form factor of their end application and increasing cost pressures associated with discrete components, assembly and production testing.

With the relentless industry drive for more sophisticated circuit functions in smaller form factors that use less power and have increased data throughput, a list of clocks source requirements has emerged. That is, clock circuits must become smaller, their operating frequency must increase and power dissipation decrease, while output jitter amplitude must be decreased and jitter frequency controlled to improve application bit error ratio, data throughput and transmission range.

Additionally, the non-recurring costs of development (i.e., initial implementation, as well as the porting of existing designs to more aggressive process nodes) and recurring costs associated with production (i.e., wafer, mask sets, fabrication, packaging,

assembly, production yield, as well as production test time, complexity and equipment) must be kept under control. All this needs to be balanced against the potential of the market (i.e., price and volume) and the cost of integration (i.e., the rarefied cost of cutting-edge processes).

One step in achieving these goals is to take a perfectly good analogue circuit operating in the s-domain and implement this same function in the digital or z-domain. This has several advantages. First, integration of many circuit functions onto a single die. This reduces form factor, as well as, manufacturing and production testing costs. Second, it improves modularity, reuse and the costs of migrating the design to other process nodes. Of course, these advantages must be weighed against the required circuit performance and power consumption. Classic examples of research and industry toiling at the boundaries of the limits of integration are low noise amplifies and power amplifiers. Specifically, there has been a great push to move these circuit functions into CMOS processes to implement a complete radio on a single chip. While this effort has been successful in many applications, CMOS noise limits low noise amplifier performance, and CMOS efficiency and output power limits power amplifier performance.

Serial-De-Serializer or SERDES circuit functions are used to concentrate many parallel communication links onto a single high-speed link. This reduces physical interconnect complexity and improves its reliability. SERDES wireline transceivers applications have evolved from system backplane to intra-die communications. This latter extreme is the application discussed in this thesis. That is, an all digital phase locked loop that provides the low-jitter clock for a SERDES transceiver used to transfer high-speed data between devices on a single die (i.e., inter-processor core or processor to memory).

This objective presents an additional set of challenges. First, analogue loop filter components, specifically capacitors, present a die real estate problem, as they do not scale with process. This is resolved by replacing the analogue filter with a digital filter, which in addition to reduced circuit size comes with benefits such as modularity, scalability and programmability. Second, the digital loop filter does not require a charge pump current source, so this element can be removed. Third, a digital phase detector is now required. The most intuitive approach is to create a circuit that resolves the smallest phase error possible, for a given process, to minimize quantization jitter and output spurs. The general approach is to use a time-to-digital

converter that produces an output vector (magnitude and direction) measurement of phase error that can be processed by the digital loop filter. A much less intuitive choice is the binary phase detector, common to receiver clock extraction circuits. The output of this circuit is a scalar value that has two stable states, speed-up and slow-down. The advantage of a binary phase detector is that it can be implemented using a single D flip-flop; thus, reducing the phase detector physical size, current consumption, scalability, portability and testability over the time-to-digital converter implementation. Its disadvantages are large quantization noise and significant output frequency-domain spurs (limit-cycle operation), limited locking range, non-linear effects and difficult analysis.

The voltage controlled oscillator is the last circuit block to be integrated with the phase locked loop components already on a single CMOS die. A fundamental challenge that must be overcome is that CMOS is noisier (both thermal and flicker noise) than other process options (i.e., SiGe, GaAs, Bipolar ...). Therefore, great care must be taken to minimize thermal and flicker noise at each step of the design process. The first step is to replace the voltage control with digital control i.e., digital controlled oscillator. A significant amount of research and development has been done recently on ring oscillators implemented using inverters. This is a solution for many of the requirements listed above; however, the low Q [8] of these oscillators makes them a difficult fit for the low-jitter digitally controlled oscillator function. LC-tank oscillators provide a much better Q (i.e., improved jitter or phase noise performance) than ring oscillators [9,10], but require a large inductor. In this work, these two options were considered and the LC-tank chosen as a reasonable compromise, the top metal layers being suitable for inductor realization. The digital-to-analogue conversion required for the digital loop filter to control the oscillator frequency was implemented directly by using an array of varactor elements that provide both frequency range and resolution. This has the additional advantage that FinFET varactor arrays are generally much smaller than Metal-Oxide-Metal/Metal-Insulator-Metal (MOM/MIM) capacitor arrays.

The Bang-Bang Phase Locked Loop derives its name from its phase detector, which as mentioned above, is a bistable implementation of the signum function. The gain between its two stable states is very high (theoretically infinite); thus, when the phase locked loop is locked, the phase detector will bang back and forth between its two stable states.

This work demonstrates how these challenges were overcome to produce a clock signal exhibiting stability and jitter performance consistent with the best analogue circuit implementation.

#### 2.2 FinFET Transistor Overview

Since circa 1970 the rate of increase in the number of transistors per unit area that can be economically fabricated to form Integrated Circuits (IC) has followed Moore's Law. That is, IC transistor densities in leading edge semiconductor technologies will double every 18 to 24 months [11,12]. His formalization has held true to the present day, and it is an understatement to say that this consistent pace of technological advancement is a tribute to the creativity, ingenuity and ability of the scientists and engineers upon whose shoulders we now stand. During the four decades proceeding Dr. Moore's paper the increased transistor density of ICs was primarily due to the aggressive scaling of planar MOSFET transistors without significant change in their basic structure.

As the Gate Length  $(L_g)$  shrinks, the MOSFET Drain Current to Gate Voltage Characteristics  $(I_d - V_g)$  degrade in two major ways, referred to as short channel effects. First, the Subthreshold Swing (S) degrades and the Threshold Voltage  $(V_t)$  decreases to the extent that the Gate Voltage  $(V_g)$  has diminished control over the channel. Second, S and  $V_t$  become increasingly sensitive to variations in  $L_g$ . Gate lengths in the nanometre range result in a drastic increase in Subthreshold Leakage Current  $(I_{off})$ . That is, the gate no longer has sufficient control to shut off the transistor at very short channel lengths because the drain potential now has increased electrostatic influence over the channel - referred to as Gate-Induced Drain Leakage (GIDL) [13, 14].

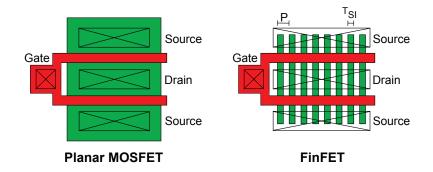

Figure 2.1 [15] presents a top-view comparison of a planar MOSFET (left) and a FinFET (right). Both devices have two gate fingers dividing the devices into Source/Drain/Source. The FinFET has eight fins with fin pitch (P) and  $T_{SI}$  is the body or fin thickness. The transistor Length (L - shown as the gate vertical dimension) and Width (W - shown as the gate horizontal dimension) of these devices correspond.

While FinFET L is a function of a single dimension, FinFET W is a function

Figure 2.1: Planar MOSFET vs. FinFET Transistors Layout

of  $2H_{FIN} + T_{SI}$ . Additionally,  $H_{FIN}$  and  $T_{SI}$  must remain fixed to ensure manufacturability, e.g.,  $H_{FIN} < 4T_{SI}$ . Therefore, arbitrary transistor widths are no longer an option. Instead W quantization is imposed, which limits the total FinFET W resolution to an integer number of fins. For example, the FinFET of Figure 2.2 has a W = 3 fins with a fin pitch of P nm. While in theory L should not be limited in this way, as L becomes smaller its values are also quantized.

Figure 2.2: Cross Section of FinFET Transistors

FinFET technology allows transistor scaling to continue without major process changes. This addition of a third dimension to the planar MOSFET gate facilitates the development of accurate mathematical models (i.e., SPICE or BSIM compact models) that seamlessly fit into existing circuit design tools.

### 2.3 SERDES Applications

Recent Serializer/Deserializer (SERDES) development has been driven by the demand for cost-effective, high-speed and high-density long-haul optical data transfer between servers, switches and routers used in data centres. Additionally, short-haul data transfer applications range from card-backplane-card over electrical and optical media, through inter-die in 2-D and 3-D packaging (e.g., Multi-Chip Modules - MCM), to intra-die over IC interconnect (e.g., interprocessor and DDR4/5 memory access) [16].

SERDES circuits are point-to-point bidirectional data transport systems consisting of a Parallel In Serial Out (PISO) transmitter and Serial In Parallel Out (SIPO) receiver positioned at opposite ends of a transmission line or fibre optic link. Thus, a large number of parallel data streams are Time Division Multiplexed (TDM) onto a much smaller number of serial data streams to reduce interconnect density, cost and complexity, as well as improve the reliability. Leading industry standard data rates include, but are not limited to, 6 Gbps, 11 Gbps, 25 Gbps, 56 Gbps and 112 Gbps using NRZ or PAM-4 modulation. Framer and packet, as well as electrical and optical physical layer interface requirements and examples can be found in [3, 16, 17].

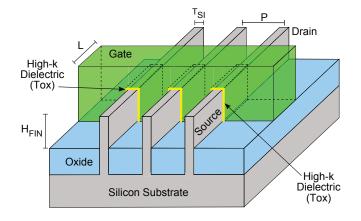

The author of this thesis was the major design and development contributor to the circuit blocks of Figure 2.3 that are not grey.

Figure 2.3 is a functional block diagram of the transmit side of the four channel SERDES device for which the ADPLL, the subject of the work, was created. The ADPLL is implemented as a Bang-Bang Phase Locked Loop (BBPLL). The 350 MHz External Clock Source [1] is commercially available and was selected for its favourable phase noise profile. The 350 MHz clock outputs, OutP/OutN, are multiplied by the BBPLL to produce 14.0 GHz differential rail-to-rail clock signals, CLKin/CLKip. These signals are buffered in the 14.0 GHz ADPLL block to drive LVDS Drivers. Two LVDS drivers are used to distribute the 14.0 GHz clock to four data transmitters and a clock transmitter through 100  $\Omega$  differential transmission lines.

The left-hand transmission line distributes the 14.0 GHz clock to Lanes one to three and the right-hand transmission line to Lanes four and five. Lanes two to five are used for data transmission and Lane one transmits the 14.0 GHz clock to the receiver in NRZ format. The transmitter circuits of each lane are identical. The 14.0 GHz differential low-voltage clock signal is tapped from the differential

Figure 2.3: SERDES Application

transmission lines by a receiver circuit within the Duty-Cycle Correction (DCC) block of each lane. Each receiver circuit consists of a series of single-ended inverters that regenerate the clock signal to its former rail-to-rail levels. Also, the single-ended regenerated signals are de-skewed using cross-coupled inverter pairs. Capacitively isolated inverters with resistive feedback are used to correct the clock duty cycle. The T-coils [18,19] are designed to tune-out the capacitance of the protection diodes and pads so the output impedance of the selected Source-Series Transmitter (SST) elements [17,20,21] are matched to the 100  $\Omega$  differential transmission line medium. This minimizes transmission line reflections, cross-talk and maximizes bandwidth. The TxP/TxN transmitter output signals terminate in substrate pads that connect, through substrate transmission lines, to the corresponding SERDES receiver.

### 2.4 Bang Bang Phase Locked Loop (BBPLL)

The purpose of a Phase Locked Loop (PLL) in this application is to multiply the frequency of an external reference clock oscillator to a higher frequency that can be used to increment the SERDES state machines and provide a timing reference for data transmission and reception. Additionally, in order to resolve transmitted data, in the presents of channel impairments, the PLL must be able to transfer the frequency stability and low Phase Noise (PN) characteristics of the external oscillator to the high frequency clock.

In recent years the ultimate goal has been to build a stable low-PN frequency multiplier around a Ring Oscillator (RO) high frequency source. The advantages of size, power dissipation, modularity and re-usability across process geometries are major. Unfortunately, for an N-stage RO, as N goes to infinity its Q approaches a maximum of  $\pi/2 = 1.57$  [9,10], which limits PN performance. By contrast, Inductor-Capacitor (LC) oscillator implementations have a higher Q (i.e., typically 10-30, depending on process losses) and a less detrimental Impulse Sensitivity Function (ISF)+ [22] than digital oscillators (i.e., Ring Oscillators - RO). While the size of the LC circuit elements is a definite drawback, they remain a viable compromise solution as their PN is expected to be lower than that of a RO by approximately 20 dB [23].

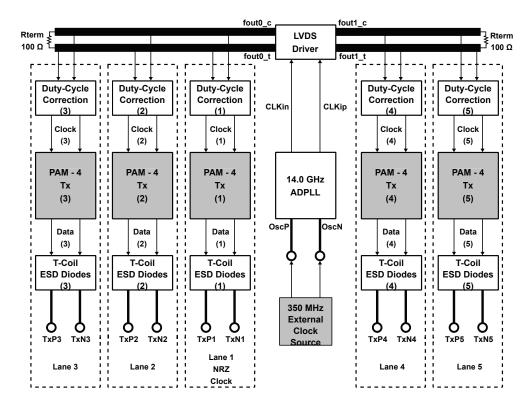

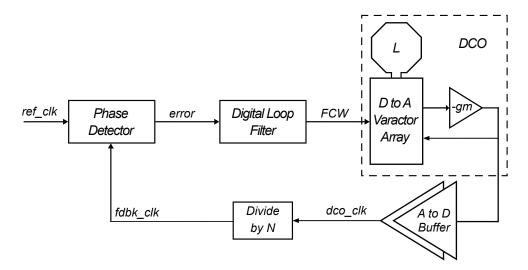

An ADPLL realized completely as a digital circuit possesses all the advantages of the RO listed previously. Thus, the DCO is the only custom designed element in this work. A digital-to-analogue conversion function must be included with the DCO to allow the ADPLL to control the analogue LC-tank oscillator phase/frequency selection. This is achieved using an array of voltage controlled capacitive elements, referred to as varactors, to realize the capacitance portion of the LC-tank - see Figure 2.4. In a DCO each varactor has two capacitive states, off-capacitance and on-capacitance, associated with the low and high voltages of the controlling bit states. Large arrays of varactors are necessary to provide the frequency tuning range required to compensate for Process, Voltage and Temperature (PVT) variations [6]. This control is generated in the forward loop form the error signal, which is low pass filtered to produce a multi-bit Frequency Control Word (FCW). The frequency tuning array design of this work is discussed in detail in section 4.4.

The DCO output clock signal must be converted from an analogue clock signal to a digital clock signal. This is achieved by buffering the analogue output of the

Figure 2.4: All Digital Phase Locked Loop with LC-Tank DCO

LC-tank oscillator to first, provide current gain to increase the slope of the rising and falling clock edges; and second, voltage limit the clock signal to produce distinct output high and low levels consistent with digital operation.

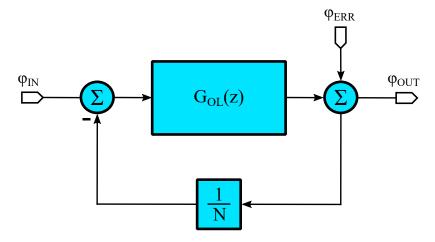

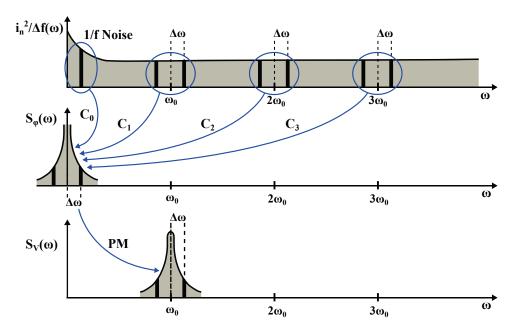

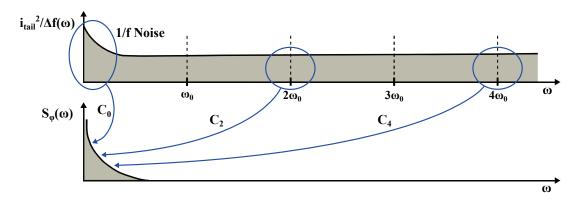

The ADPLL shown in Figure 2.4 possess two quantization noise sources - the Phase Detector (i.e., Time-to-Digital Converters - TDCs, Binary Phase Detectors ...) and the D to A function of the DCO. These are not present in analogue PLLs with nearly-continuous phase detectors (excluding dead zones) and linear VCO tuning curves. The finite phase/frequency steps that are generated by this quantized behaviour produce a limit-cycle mode of operation or regime in the output clock, dco\_clk, when the ADPLL approaches a phase locked state. That is, as the output frequency of the DCO will almost certainly not be an exact multiple of the reference frequency, ref\_clk; therefore, the phase detector will force a frequency oscillation about the exact multiple. This oscillation or frequency modulation will produce significant frequency-domain spurs at the dco\_clk output. In this work it will be demonstrated that an ADPLL realized as a BBPLL (i.e., Bang-Bang Binary Phase Detector - BBPD) can be designed to meet and exceed the performance of analogue PLL implementations, in spite of additional quantization noise sources. The BBPD has the additional advantages of reduced circuit complexity and power consumption when compared to TDC implementations. A trade-off between quantization noise and random thermal noise can be achieved by adjusting the proportional gain of the loop filter to find a total output PN minimum. Additionally, thermal noise can be used to both linearize the phase detector quantization and redistribute the frequency-domain spur energy into the noise floor.

What is a Bang-Bang PLL or, where does the bang bang come from - doesn't every PLL operate in this way? These questions can be answered by first defining what is PLL limit-cycle operation. Many PLLs can operate in a limit-cycle mode or regime. This happens when the feedback control loop reaches a locked state where the output frequency (or phase) oscillates about a fixed value. That is, when the DCO or Phase-Frequency Detector (PFD) have finite resolution and this resolution is periodically exceeded. Therefore, if the feedback frequency is too high, the phase detector will tell the loop to reduce frequency, and after this new reduced frequency is compared the phase detector the resulting error will adjust the oscillator to increase frequency. If the frequency and amplitude of these limit-cycles are small enough, this operation may be considered acceptable. However, in a Band-Bang PLL this is a dominant behaviour. In fact it is the extreme form of this behaviour that gives this PLL its name. Most phase or phase-frequency detectors (i.e., Time-to-Digital Converter, phase detector charge pump combinations, XOR ...) provide a vector output consisting of phase error sign and amplitude. In contrast, the binary phase detector output is a scalar consisting of phase error sign only. That is, it always tells the loop to apply a maximum correction no matter the phase error. This causes the Bang-Bang PLL to exhibit limit-cycle behaviour in the absence of other dominating phenomena, such as random phase noise, after it is locked. This mode of operation results in quantization noise and spurs at the output.

The current state of BBPLL development has minimized the BBPD to a two-state signum (i.e.,  $sgn(\Delta t)$  error function realized as a single D flip-flop; therefore, that is what is used here. Figure 2.5 shows the architecture of a generalized Bang-Bang Phase Locked Loop (BBPLL) [24].

The functional block diagram of Figure 2.5 is described in detail in the chapters that follow, so only a brief introduction is presented here. A highly stable low PN external crystal oscillator generates the  $ref\_clk$  (e.g., 350 MHz) for the PLL. The  $ref\_clk$  phase is compared by the BPD to the phase of the feedback clock,  $fdbk\_clk$ , which is a frequency divide by N version of the DCO output clock,  $dco\_clk$ . This comparison produces a highly quantized binary error,  $sgn(\Delta t)$ , that is presented to the weighted (i.e.,  $A_p$  and  $A_i$ ) proportional plus integral paths of the Digital Loop Filter (DLF). The DLF is clocked by  $fdbk\_clk$ . The  $z^{-D}$  block represents the delay, in

Figure 2.5: Bang Bang Phase Locked Loop

$D\ fdbk\_clk$  cycles, in the forward loop that will occur due to circuit implementation. The filtered DCO Frequency Control Word (FCW) produced by the DLF is split into higher order and lower order paths. The higher order bits control the DCO frequency selection directly, while the lower order bits feed an  $n^{th}$  order  $\Sigma\Delta$ -modulator. The  $\Sigma\Delta$ -modulator creates a dithered average frequency selection that improves the DCO resolution while minimizing the production of  $dco\_clk$  frequency-domain spurs.

In this work a significant amount of attention was paid to ensuring that the last remaining analogue portion of the BBPLL, the DCO frequency generation, would function over PVT as well as extracted layout variations. Additionally, care was taken to reduce PN, particularly flicker noise.

#### Chapter 3

# The Bang Bang Phase Locked Loop

#### 3.1 Introduction

The following list identifies the advancements made through the development of this BBPLL, excluding the DCO, which is discussed in chapter 4.

- 1. Oversampling of the reference clock by the feedback clock at the phase detector was used to reduce the noise bandwidth of the system. That is, a feedback divisor of N=4 was used instead of the N=40, required to make the reference and feedback clock frequencies approximately equal. This limits the amount of noise that can be imposed on the loop.