**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company

300 North Zeeb Road, Ann Arbor MI 48106-1346 USA

313/761-4700 800/521-0600

# A Comprehensive Design Method for Dual Gate MOSFET Mixers

by **Adrian John Bergsma, B.Eng.**

A thesis submitted to

the Faculty of Graduate Studies and Research

in partial fulfillment of

the requirements for the degree of

Master of Engineering

Ottawa Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

Ottawa, Canada

May 1998

© 1998 AJ Bergsma

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reference

Our file Natre reference

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-32392-7

# The undersigned hereby recommend to the faculty of Graduate Studies and Research acceptance of the thesis

A Comprehensive Design Method

for

Dual Gate MOSFET Mixers

submitted by Adrian John Bergsma, B.Eng.

in partial fulfillment of the requirements for the degree of Master of Engineering

Chair, Department of Electronics

Thesis Supervisor

Carleton University May 1998

#### Abstract

A comprehensive design method for a dual gate MOSFET mixer is proposed providing a simple, practical, methodical approach to predict the gain and input compression point of a DGFET mixer with each step in the process being easily implemented by either simulation or lab bench techniques. It also provides an accurate, understandable procedure for identifying and verifying the appropriate bias conditions and the minimum LO power level required.

Using a discrete packaged device, a dual gate mixer core structure is fully characterized for conversion gain and input compression point. A single-balanced dual gate MOSFET mixer circuit is constructed and measured with an RF input frequency of 857 MHz, LO frequency of 694 MHz, and an IF output frequency of 163 MHz.

The final mixer exhibits 5.4 dB conversion gain and an input compression point of -9 dBm. When the external matching networks are accounted for, the mixer core structure exhibits 11.9 dB of conversion gain and an input compression point of 3 dBm.

The information in this thesis comes in part from the research program of Dr. Barry Syrett. The research results appearing in this thesis represent an integral part of the ongoing research program. All research results in this thesis, including tables, graphs, and figures but excluding the narrative portions of the thesis are effectively incorporated into the research program and can be used by Dr. Syrett and his associates for education and research purposes only, including publication in the open literature with appropriate credits to Adrian John (A.J.) Bergsma. Matters of intellectual property may be pursued with Carleton University and Dr. Syrett where and when appropriate.

#### Acknowledgments

I would like to take the opportunity to thank Professor Barry Syrett for his assistance in the completion of this thesis and the degree program. The constructive discussions, the attention to detail, the expectation of excellence, and the willingness to help in all areas of the program were greatly appreciated.

I would also like to gratefully acknowledge the significant contribution of John Nisbet of Nortel who constructively enabled the rapid completion of the thesis by providing the environment that proved to be required to handle both work and academic pursuits simultaneously.

I would like to acknowledge and thank Johan Grundlingh of Nortel for providing an interesting, interactive learning environment by listening and discussing the theoretical basis for the design method as it matured. His insights into the practical requirements of the design as well as the physical implementations of the circuitry were invaluable.

I would like to thank my parents, Jerry and Dianne Bergsma, for all of the help, support, and understanding over the years, without which I would have never been able to make the vision a reality. Thank you very much.

I would also like to thank Lisa and Alexandra who were instrumental in helping me complete the degree program. I can not even begin to describe the multitude of ways that you two have helped as we finished this degree together.

# **Table of Contents**

| List of | Figures and Tablesvi                       |

|---------|--------------------------------------------|

| List of | Abbreviations and Acronymsx                |

| Chapte  | r 1: Introduction1                         |

| 1.1     | Introduction1                              |

| 1.2     | Thesis Outline                             |

| 1.3     | Thesis Contributions 4                     |

| Chapte  | r 2: System Considerations5                |

| 2.1     | System and Specification Overview5         |

|         | 2.1.1 System Architecture5                 |

|         | 2.1.2 Mixer Specifications                 |

| 2.2     | Technology Issues                          |

|         | 2.2.1 The One Chip Radio Challenge10       |

|         | 2.2.2 MOSFET Process Technology Background |

| 2.3     | RFIC Mixer Circuit Topologies 14           |

|         | 2.3.1 BJT Base and FET Gate Mixers         |

|         | 2.3.2 Tree or Gilbert Cell Mixers          |

|         | 2.3.3 FET Drain Mixers                     |

|         | 2.3.4 FET Ring Mixers                      |

|         | 2.3.5 FET Dual Gate Mixers 19              |

| 2.4     | Summary                                    |

| Chapter 3: The Dual Gate FET                           | 24                |

|--------------------------------------------------------|-------------------|

| 3.1 The Dual Gate Structure                            | 24                |

| 3.2 Modeling Concerns                                  | 27                |

| 3.2.1 The Single Gate MOSFET                           | 27                |

| 3.2.2 The Dual Gate MOSFET                             | 28                |

| 3.2.3 The Cascode Approximation                        | 30                |

| 3.3 Summary                                            | 31                |

| Chapter 4: Design Methodologies                        | 32                |

| 4.1 Design Methodology Requirements                    | 32                |

| 4.2 Current State of the Art                           | 34                |

| 4.2.1 Harmonic Balance and Large Signal - Small Signal | Techniques34      |

| 4.2.2 Dual Gate FET Mixer Design Methodologies         | 36                |

| 4.2.2.1 Dual Gate MOSFET Method: Kleinman              | 36                |

| 4.2.2.2 Dual Gate MESFET Method: Tsironis, Mei         | erer, Stahlman37  |

| 4.2.2.3 Microwave Mixer Methods: Maas                  | 38                |

| 4.2.3 Drain Mixer Methodologies                        | 39                |

| 4.2.3.1 MESFET Drain Mixer Method: Begemann,           | Jacob40           |

| 4.2.3.2 MESFET Drain Mixer Method: Cayrou, Ga          | yral, Graffeuil41 |

| 4.3 Proposed Design Method                             | 41                |

| 4.3.1 Features of Proposed Design Method               | 41                |

| 4.3.2 Theoretical Background                           | 43                |

| 4.3.2.1 Introduction                                   | 13                |

| 4.3.2.2 Equations for Gain Calculation43                           |

|--------------------------------------------------------------------|

| 4.3.2.3 Method for Calculation of Input Compression Point          |

| 4.3.3 Concise Summary of Method                                    |

| 4.4 Summary49                                                      |

| Chapter 5: Application of the Method51                             |

| 5.1 A Characterization Example                                     |

| 5.1.1 Determination of Bias Conditions                             |

| 5.1.1.1 Device Selection                                           |

| 5.1.1.2 DC Characteristics                                         |

| 5.1.1.3 The gm2 Function                                           |

| 5.1.1.4 The $\Delta gm2$ Function                                  |

| 5.1.1.5 Bias Selection                                             |

| 5.1.2 Determination of RF Characteristics                          |

| 5.1.2.1 Steady State Condition and $\Delta gm2 _{f_{lo}}$ function |

| 5.1.2.2 Conversion Transconductance                                |

| 5.1.2.3 Verification of LO Bias Selection                          |

| 5.1.2.4 Input Compression Point                                    |

| 5.2 Summary                                                        |

| Chapter 6: Design Optimization and Results68                       |

| 6.1 Generalization of the Design Method                            |

| 6.1.1 Effect of RF Bias and LO Power on Mixer Characteristics69    |

| 6.1.1.1 Gain Characteristics                                       |

|        | 6.1.1.2 Input Compression Point                                 | 71  |

|--------|-----------------------------------------------------------------|-----|

|        | 6.1.1.3 Third Order Intercept Point                             | 73  |

|        | 6.1.1.4 LO Compression                                          | 74  |

|        | 6.1.2 Effect of LO Bias and LO Power on Conversion Gain         | 76  |

|        | 6.1.3 Summary of Effect of Bias Conditions on Mixer Performance | 77  |

| 6.2    | 2 Design Completion                                             | 78  |

|        | 6.2.1 Design Criteria                                           | 78  |

|        | 6.2.2 Port Impedance Selection                                  | 79  |

|        | 6.2.2.1 The LO Input Port                                       | 79  |

|        | 6.2.2.2 The RF Input Port                                       | 80  |

|        | 6.2.2.3 The IF Output Port                                      | 80  |

| 6.3    | The Complete Mixer                                              | 81  |

|        | 6.3.1 The Mixer Circuit                                         | .81 |

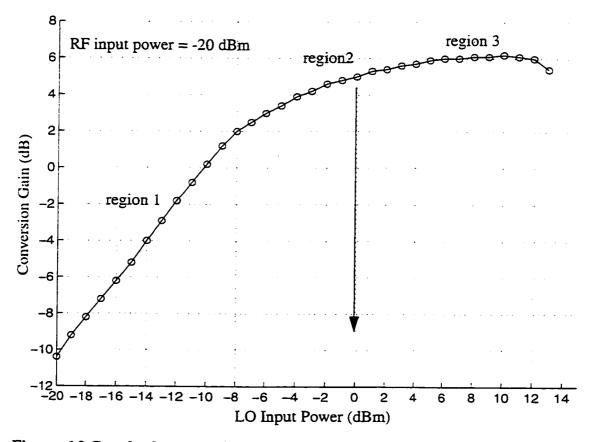

|        | 6.3.2 LO Power Selection                                        | .82 |

|        | 6.3.3 Final Mixer Conversion Gain Characteristics               | .84 |

| 6.4    | Complete Mixer Results and Comparisons                          | .87 |

| 6.5    | Summary                                                         | .89 |

| Chapte | r 7: Conclusions and Recommendations                            | .91 |

| 7.1    | Thesis Summary                                                  | .91 |

| 7.2    | Conclusions                                                     | .91 |

| 7.3    | Future Work                                                     | .93 |

|        | 7.3.1 Noise Figure                                              | .93 |

| 7.3.2 Optimization of Device Dimensions      | 93  |

|----------------------------------------------|-----|

| Appendix A: Theoretical Background Equations | 95  |

| A.1 The Taylor Series                        | 95  |

| A.2 The Design Method Approach               | 96  |

| References                                   | 101 |

# List of Figures and Tables

| Chapter | 2 |

|---------|---|

|         |   |

| Figure 2.1 | a) Typical receiver architecture6                    |

|------------|------------------------------------------------------|

|            | b) Typical transmitter architecture                  |

| Figure 2.2 | MOS gate mixer structure                             |

| Figure 2.3 | MOS tree mixer structure                             |

| Figure 2.4 | MOS drain mixer structure                            |

| Figure 2.5 | MOS ring mixer structure                             |

| Figure 2.6 | a) Unbalanced dual gate mixer structure21            |

|            | b) Balanced dual gate mixer structure21              |

|            |                                                      |

| Chapter 3  |                                                      |

| Figure 3.1 | a) Generic MOS single gate physical representation25 |

|            | b) Generic MOS single gate schematic symbol25        |

|            | c) Simplified MOS single gate small signal model25   |

| Figure 3.2 | a) Generic MOS dual gate physical representation     |

|            | b) Generic MOS dual gate schematic symbol            |

|            | c) Simplified MOS dual gate small signal model 26    |

# Chapter 5

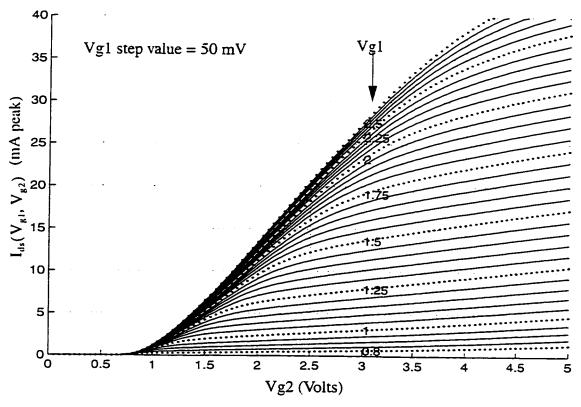

| Figure 5.1  | Graph of measured DC drain current as a function of $V_{g2}$ for stepped                    |

|-------------|---------------------------------------------------------------------------------------------|

|             | values of $V_{g1}$ 53                                                                       |

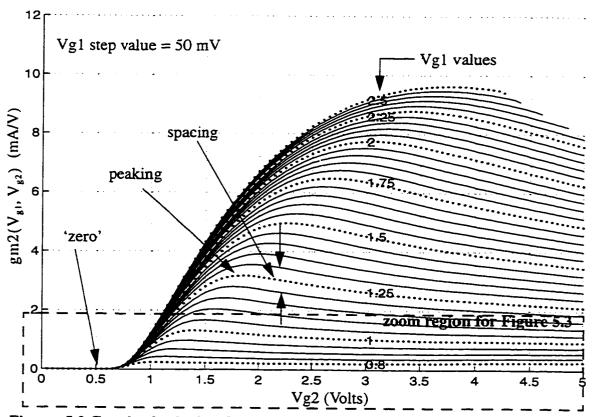

| Figure 5.2  | Graph of calculated $gm2$ as a function of $V_{g2}$ with stepped $V_{g1}$ 54                |

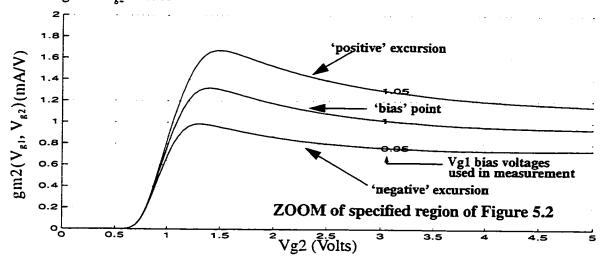

| Figure 5.3  | Close up graph of $gm2$ as a function of $V_{g2}$ for representative RF bias                |

|             | condition showing excursions from the bias point55                                          |

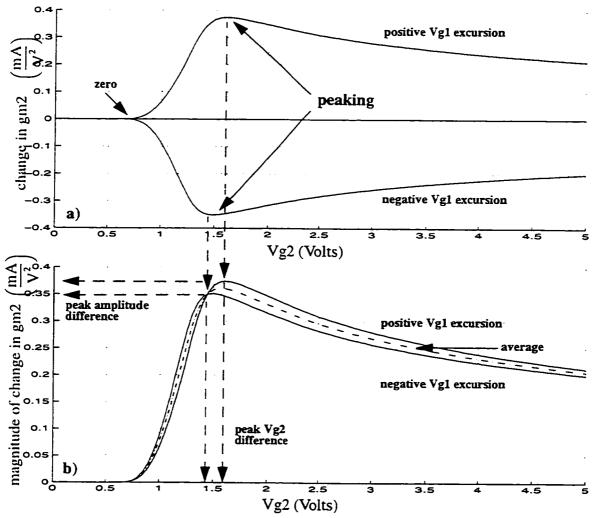

| Figure 5.4  | a) Graph of change in $gm2$ caused by a shift in RF bias normalized to the                  |

|             | bias point as a function of $V_{g2}$ 56                                                     |

|             | b) Graph of magnitude of change in $gm2$ as a function of $V_{g2}$ to clarify               |

|             | differences between positive and negative RF excursions56                                   |

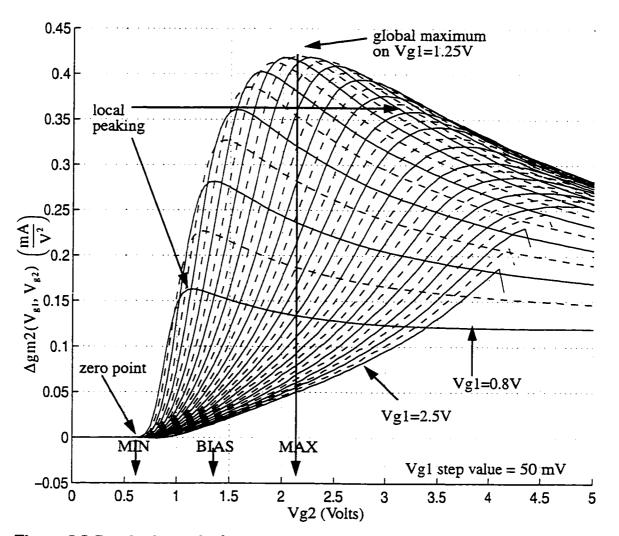

| Figure 5.5  | Graph of $\Delta gm2$ , the average change in $gm2$ , as a function of $V_{g2}$ for         |

|             | stepped values of $V_{g1}$ showing details for bias selection                               |

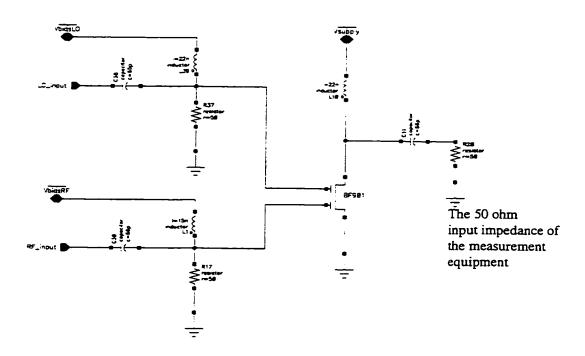

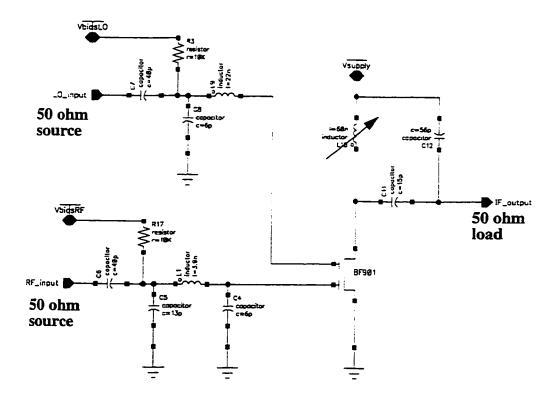

| Figure 5.6  | Schematic of circuit used for characterization with 50 ohm port                             |

|             | impedances60                                                                                |

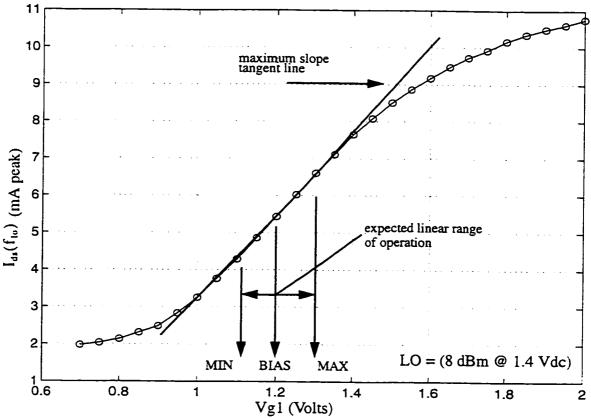

| Figure 5.7  | Graph of LO frequency output current as a function of $V_{g1}$ 61                           |

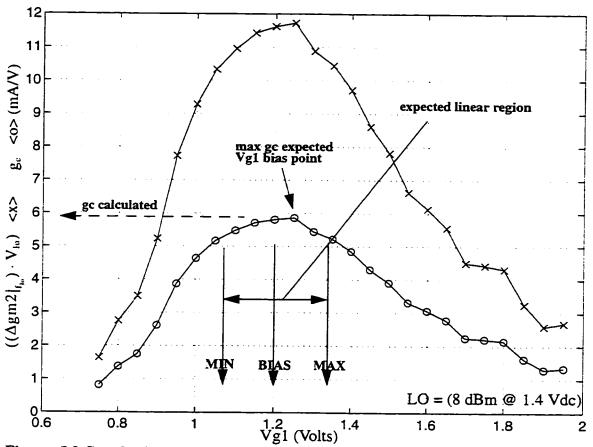

| Figure 5.8  | Graph of calculated conversion transconductance and $((\Delta gm2 _{f_{lo}}) \cdot V_{lo})$ |

|             | as a function of RF bias $(V_{g1})$ 62                                                      |

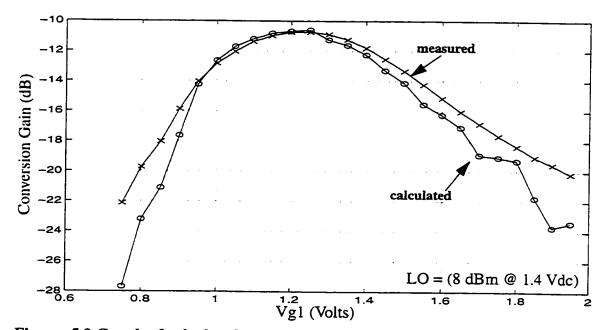

| Figure 5.9  | Graph of calculated and measured conversion gain as a function of RF                        |

|             | bias voltage ( $V_{g1}$ ) with 50 ohm load63                                                |

| Figure 5.10 | Graph of measured conversion gain as a function of LO bias with 50 ohm                      |

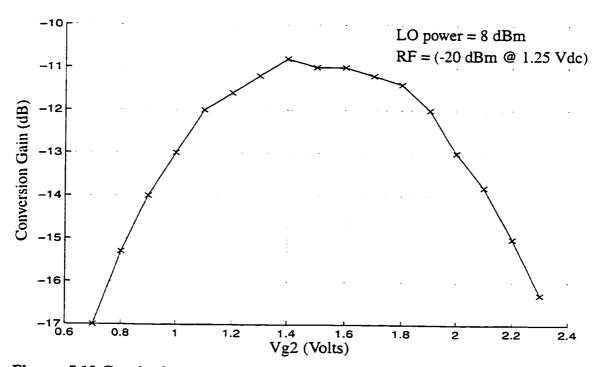

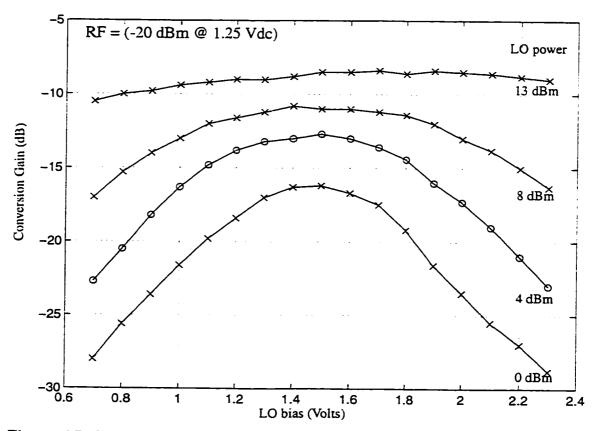

|             | load64                                                                                      |

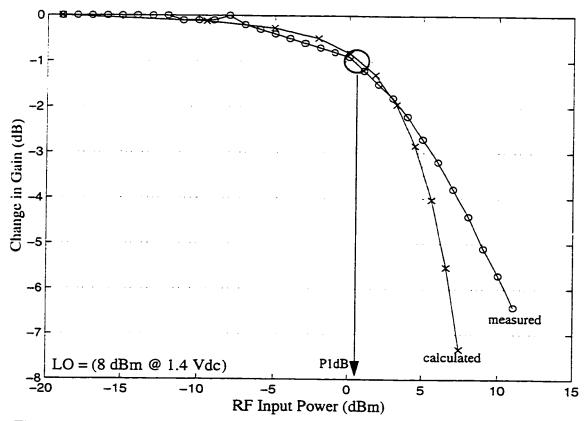

| Figure 5.11 | Graph of calculated and measured conversion gain compression as a         |

|-------------|---------------------------------------------------------------------------|

|             | function of RF input power with 50 ohm load                               |

| Chapter 6   |                                                                           |

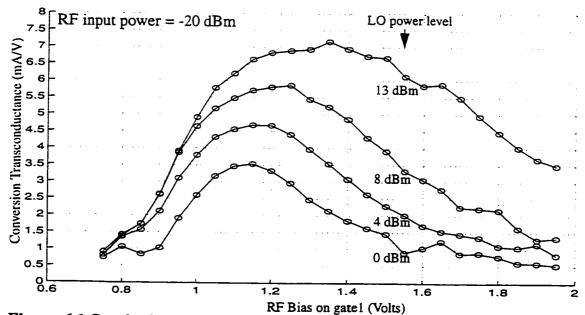

| Figure 6.1  | Graph of conversion transconductance as a function of RF bias for various |

|             | LO power levels69                                                         |

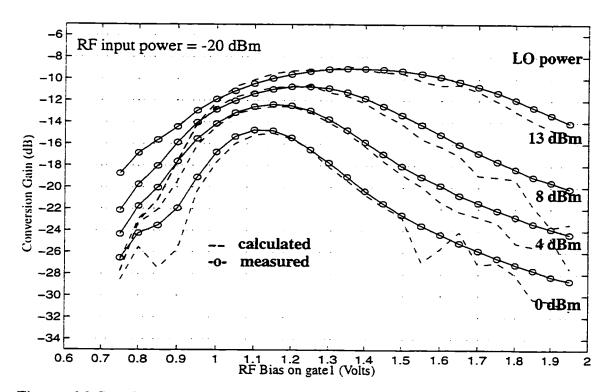

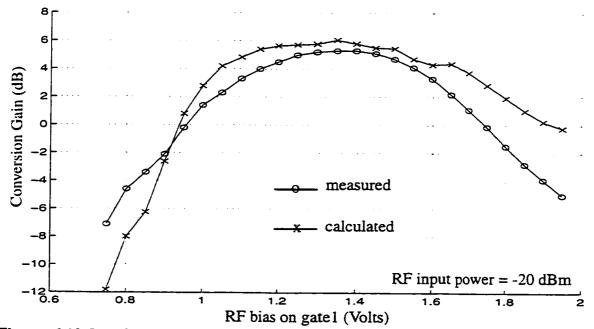

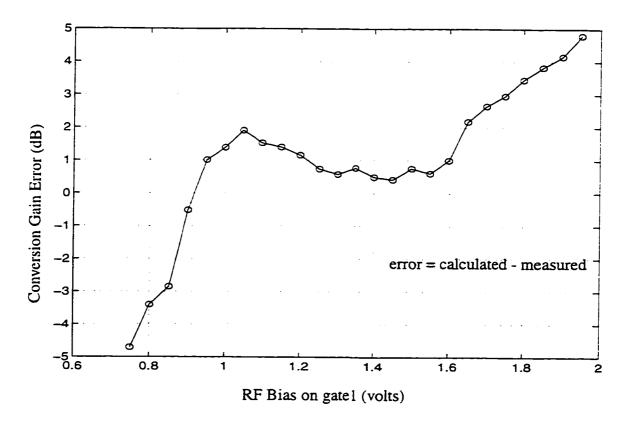

| Figure 6.2  | Graph of calculated and measured conversion gain as a function of RF      |

|             | bias for various LO power levels70                                        |

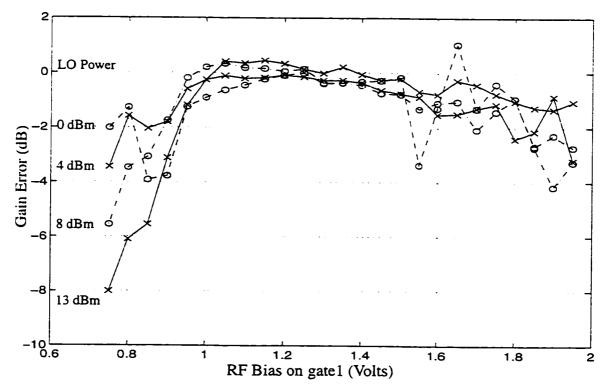

| Figure 6.3  | Graph of conversion gain error as a function of RF bias for various LO    |

|             | power levels71                                                            |

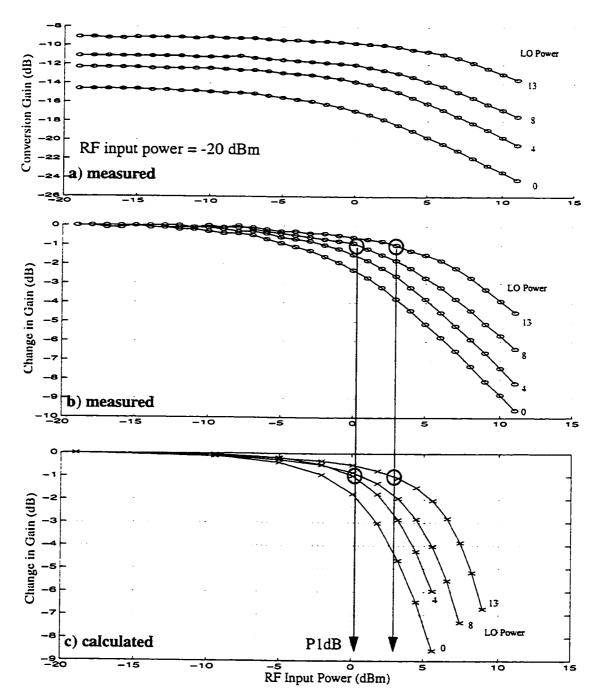

| Figure 6.4  | a) Graph of measured conversion gain as a function of RF input power for  |

|             | various LO power levels72                                                 |

|             | b) Graph of measured gain compression as a function of RF input power     |

|             | for various LO power levels72                                             |

|             | c) Graph of calculated gain compression as a function of RF input power   |

|             | for various LO power levels72                                             |

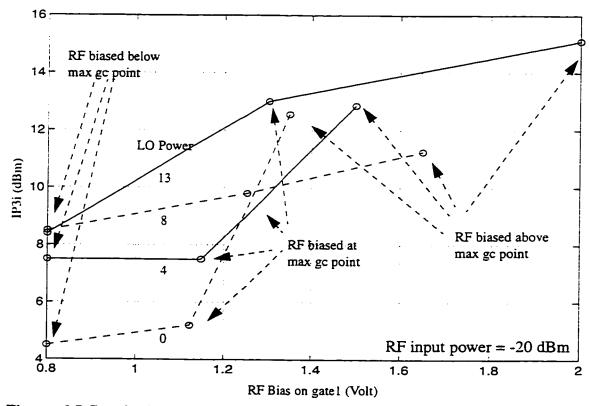

| Figure 6.5  | Graph of input third-order intercept characteristics as a function of RF  |

|             | bias for various LO power levels                                          |

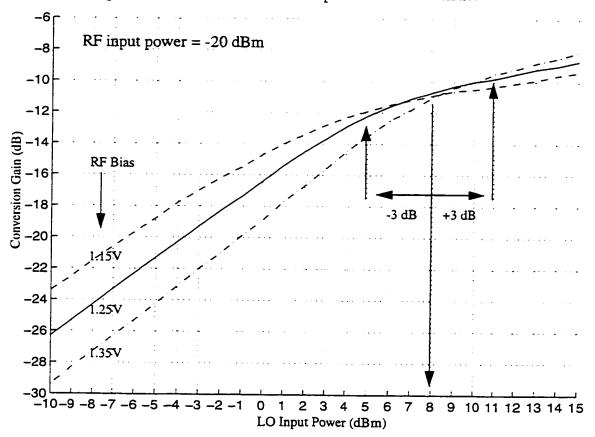

| Figure 6.6  | Graph of conversion gain as a function of LO drive level for various RF   |

|             | bias conditions                                                           |

| Figure 6.7  | Graph of conversion gain as a function of LO bias for various LO power    |

|             | levels                                                                    |

| Figure 6.8  | Schematic of final mixer circuit used for measurements8                   | 2 |

|-------------|---------------------------------------------------------------------------|---|

| Figure 6.9  | Graph of measured conversion gain as a function of LO drive level for the |   |

|             | final mixer8                                                              | 4 |

| Figure 6.10 | Graph of calculated and measured conversion gain as a function of RF      |   |

|             | bias for the final mixer8                                                 | 5 |

| Figure 6.11 | Graph of conversion gain error as a function of RF bias for the final     |   |

|             | mixer                                                                     | 5 |

|             |                                                                           |   |

| Table 6.1:  | Table of designed mixer characteristics including comparisons with other  |   |

|             | dual gate mixers88                                                        | 3 |

# List of Abbreviations and Acronyms

ADC Analog to digital converter

AGC Automatic gain control

BJT Bipolar junction transistor

CAD Computer aided design

CDMA Code division multiple access

DAC Digital to analog converter

DC Direct current

DGFET Dual gate field effect transistor

DRC Design rule check (a design verification tool)

EMI Electromagnetic interference

FET Field effect transistor

GaAs Gallium arsenide

HB Harmonic balance analysis method

IC Integrated circuit

IF Intermediate frequency

IP3 Third order intercept point

LNA Low noise amplifier

LO Local oscillator

LS-SS Large signal - small signal analysis method

LVS Layout versus schematic (a design verification tool)

MOSFET Metal oxide semiconductor field effect transistor

P1dB One dB compression point

PA Power amplifier

PLL Phase locked loop

RF Radio frequency

RFIC Radio frequency integrated circuit

TDMA Time division multiple access

VCO Voltage controlled oscillator

gm2 the nonlinear function that represents the pseudo-transconductance of the

dual gate device from gate 2 to drain.

$\Delta gm2$  the nonlinear function that represents the sensitivity of the gm2 function

to the input signal. It is related to the conversion transconductance.

$g_c$  the conversion transconductance from RF input voltage to IF output

current.

# **Chapter 1: Introduction**

#### 1.1 Introduction

The consumer demand for low cost, high quality, mobile communications services has resulted in continued growth for the telecommunications industry[1.1]. In order to maximize the efficient use of available spectrum as well as provide improved services, digital transmission techniques such as TDMA and CDMA have become the dominant communication standards. The use of digital communication methods has provided the means for a convergence in the methods of treating already digital computer traffic and the now digitized voice traffic.

While most of the active components dealing with the high frequency signal transmission and reception functions are done with either bipolar or MESFET technologies, most digital processing is done with the significantly less expensive, low power MOS technology. Significant cost savings could result if the radio system, from transmission and reception to data processing, could be completely integrated on one chip in one technology. Although this is economically attractive, there are serious technological hurdles to overcome before this can become a commonplace reality [1.2 to 1.8].

Although the complete integration of the radio system on one chip may not currently be feasible, there is also a growing economic benefit of a general cost reduction in terms of the discrete parts used to create the radio system. The use of MOS devices for the high frequency analog sections of radio systems and the economies of scale made possible by the use of the lower cost MOS technologies, already used for mass production of

digital circuits, may provide significant system level cost reductions without a reduction in quality or reliability.

To address the concerns and questions about the high frequency capabilities of the MOS technologies, significant research is continuing into the high frequency characteristics of MOS technologies to determine whether they are suitable for high frequency applications in the transmission and reception sections of modern communication systems [1.9 to 1.15]. Along with new radio system architectures and methods, research is continuing into integrated circuit structures and topologies for amplifiers, filters, dividers, oscillators and mixers. It is the aim of this thesis to add to this growing body of knowledge.

#### 1.2 Thesis Outline

This thesis is organized into seven chapters. The first chapter provides a general introduction to the current technological and economic situation which provided the impetus for the development of the design procedure described in the thesis as well as an outline and the thesis contributions to the topic.

Chapter two reviews the system considerations such as architecture and specifications followed by a discussion of the technological challenges specific to the use of MOSFETs in high frequency analog applications. A review of some of the basic radio frequency integrated circuit (RFIC) mixer circuit topologies provides a background for the circuit topologies currently available to the RFIC designer.

Chapter three explains the dual gate FET structure followed by a discussion of some of the modeling concerns for single as well as dual gate MOSFETs. The 'cascode approximation' and its usefulness in the context of design and modeling is explained.

Chapter four is concerned with describing the design methodologies currently available for dual gate mixers. A brief introduction to the harmonic balance and large signal/small signal analysis techniques is followed by summaries of some key design approaches currently available in the literature. Following this review, the proposed design method is described using a brief theoretical introduction, the mathematical equations used in the method, and then a concise summary to clarify the simplicity of the method.

Chapter five deals with the detailed practical application of the design method. Each step of the method is described in detail along with the practical aspects of implementing each step. It is structured to closely follow an expected design procedure and includes all of the required DC and RF data from one characterization example including the determination of bias conditions as well as the calculation of conversion transconductance and input compression point.

Chapter six further explores the characterized circuit and provides the extra information needed by the designer for intelligent optimization of the final design. The discussion and results showing the effects of RF bias and LO power levels on the mixer circuit are invaluable tools and illustrate the flexibility available to the designer as well as the accuracy of the design method over various bias and power conditions. Using the results of this exploration, a final mixer is designed with the results being tabulated and a brief comparison being made to other similar dual gate structures.

Chapter seven provides the conclusions that can be drawn from this thesis and gives some areas that can be explored for future work.

#### 1.3 Thesis Contributions

This thesis seeks to expand the knowledge base for the use of MOS technologies in high frequency communication circuits by providing a practical, systematic, theoretically sound method to accurately design a dual gate MOSFET mixer. Applications include, but are not restricted to, the high frequency or intermediate frequency portions of wireless systems, cable TV systems, and computer modems.

Although the dual gate field effect transistor (DGFET) has been in use for a number of years, its operation is significantly more complex than a single gate transistor with its true behaviour being difficult to model effectively. This has left the designer with insufficient details concerning the operation of the device to properly design circuits with the device. This results in empirical designs with often disappointing characteristics, or the avoidance of designing with the device at all.

The method proposed in this thesis provides a solution for this situation by providing a design method that employs a simple, practical, methodical approach to calculate the gain and input compression point of a DGFET mixer with each step in the process being easily implemented by either simulation or lab bench techniques. It provides an accurate, understandable procedure for identifying and verifying the appropriate bias conditions and also provides the means to define the minimum LO power level required. The technique is aimed at producing a well engineered design, not a rigorous numerical solution.

# **Chapter 2: System Considerations**

Mixers are used in radio communication systems to translate signals from one frequency to another so that information signals can be more effectively processed. Proper mixer design can be critical to the success of a communication system as the characteristics of the mixer can often be the limiting factor in a communication system[2.1]. This discussion will concentrate on the implementation of mixers in a radio frequency integrated chip (RFIC) environment.

#### 2.1 System and Specification Overview

## 2.1.1 System Architecture

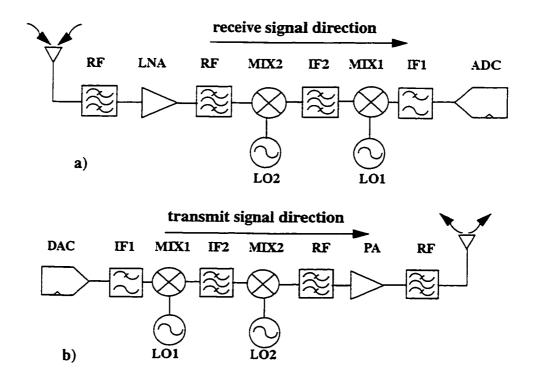

A representation of a generic modern receiver architecture is shown in Figure 2.1. The receiver consists of an input, for example an antenna or cable system, an RF filter for selecting the radio frequency (RF) band desired, a low noise amplifier (LNA), another RF filter, a mixer (MIX2) driven by the local oscillator (LO2), a filter at the intermediate frequency (IF2), another mixer (MIX1) driven by the first LO (LO1), followed by a low pass filter (IF1) and an analog to digital converter (ADC). This system translates the information in the RF signal to a lower frequency where it can be more effectively digitized for further processing.

The transmitter is similar in architecture to the receiver, but with a reversed signal path. It converts the digitized information into an analog signal and translates the information signal, with appropriate filtering, to a higher frequency where it can be more

easily transmitted by an antenna or cable system, using a power amplifier (PA) to obtain the transmit power required.

Figure 2.1 a) Typical receiver architecture b) Typical transmitter architecture

# 2.1.2 Mixer Specifications

Mixers generally make use of the trigonometric identity shown in Equation 2.1. The multiplication of two frequencies together creates frequency components at the sum and difference frequencies, only one of which is usually desired. Normally, the equation that describes the operation of the circuit is much more complex than a simple cosine multiplication, resulting in many extra frequency components. Filtering of the output not

only selects the desired sideband, but is helpful in reducing extraneous frequency components at the output.

$$\cos(2\pi f_1 t) \times \cos(2\pi f_2 t) = \frac{1}{2} \left( \cos(2\pi (f_1 + f_2)t) + \cos(2\pi (f_1 - f_2)t) \right) \tag{2.1}$$

A perfect mixer performs this frequency translation with no modification or distortion of the information in the signal, no signal strength loss, no dependence upon the amplitude of the LO waveform, and no addition of noise. Ideally, the only output would be the frequency desired, with no components of the local oscillator frequency, the original signal frequency, or any other undesired frequencies. Real mixers differ on how well they approach this ideal, resulting in specifications for linearity, noise figure, signal handling capabilities, LO compression, and port isolation. A brief review of these specifications will help illustrate the challenges involved.

Signal handling capabilities are often discussed in terms of the one dB compression point, or P1dB. As the input signal power increases, the circuit can no longer process the signal correctly without distortion. One result of this is a reduction in gain. The P1dB value identifies the input power at which the circuit gain is one dB lower than the expected gain. In a receiver, a high P1dB point allows a circuit to withstand multiple input signals without distortion, providing a measure of immunity from blocking signals, desensitization, and signal power fluctuations. In a transmitter, a high P1dB point allows for increased signal to noise ratios and more efficient use of the circuit.

The third-order intercept point, or IP3, is a measure of the linearity of the system. Third-order distortion results from nonlinearities in the circuit that cause the multipli-

cation of the desired input signal with adjacent channel signals, creating distortion products that are close in frequency to the original desired signal. Due to this proximity in frequency, third-order products cannot be filtered out and, once created, remain in the system causing distortion and errors. In a receiver, a high IP3 may allow the relaxation of filtering requirements as well as provide a measure of protection against large adjacent signals causing distortion in the radio.

Noise figure is a measure of how much noise the circuit adds to the signal as it passes through the circuit, or alternatively, the change in the signal to noise ratio through the circuit. Each circuit topology has different noise characteristics depending upon inherent device and technology capabilities as well as circuit structure. Mixer noise contributions can be a significant portion of the system noise floor. In a receiver, this places a lower limit on the minimum receivable signal power. In a transmitter, the noise floor can be transmitted as sidebands, creating interference for adjacent channels. Minimum noise figure is beneficial in reducing these effects.

The LO compression characteristic is a measure of the immunity of the mixer gain to variations in the amplitude of the LO waveform. This is commonly described by the ratio of change in mixer gain to the change in LO power, with the ideal case being a ratio of zero. At low LO power levels, mixers can exhibit 1 dB of gain variation for 1 dB change of LO power, resulting in a high sensitivity to the LO power level. As the LO waveform may arrive at the mixer input through a series of amplifiers and filters, each with its own temperature and process variation, a mixer that is highly dependent upon the LO input waveform becomes susceptible to large temperature and process variation which could lead to specification failures due to a cascading effect at the system level.

Port isolation is a measure of frequency component suppression between ports. Mixer circuit topologies are described as unbalanced or single-balanced, double-balanced, or fully balanced. Balanced circuits use the relative phase of the signals to provide suppression of the input signals and enhancement of the output signal at the output port of the circuit. Some circuit topologies provide inherent isolation between the LO and RF ports, although many do not. The degree of port isolation possible with any given technology or circuit topology is often dependent upon parasitic effects such as capacitive coupling and device mismatch. Port isolation is very important at the system design level as it impacts directly on the amount of filtering required before and after the mixer. For example, in some systems, a significant LO frequency component at the output of the mixer is unacceptable as it causes compression and distortion in the following amplifier or spurious frequency generation or transmission elsewhere in the system. Increased filtering may not be an acceptable solution as filtering can cause increased signal loss, distortion through filter gain ripple and phase delays, and increased manufacturing costs. As such, port isolation can be a determining factor in the choice of circuit topology.

Once the specifications for linearity, noise figure, signal handling capabilities, LO compression, and port isolation are decided, the circuit designer must choose how to approach the design by investigating process technologies, circuit topologies, and design tools or methods that will provide a cost effective solution.

#### 2.2 Technology Issues

### 2.2.1 The One Chip Radio Challenge

The increasing consumer demand for high quality mobile communication capabilities provides a compelling economic impetus to investigate innovative technological solutions to reduce the cost of providing communication services. Consumer interest is increasingly concentrated on mobility, low cost, and speed and reliability of transmission. In order to address these concerns, system designers have reduced supply voltage levels to reduce the size, weight, and cost of mobile units, have used digital transmission techniques such as TDMA and CDMA to improve the signal transmission reliability and quality, and have improved digital signal processing capabilities in order to be able to provide enhanced consumer services.

A significant source of electromagnetic interference (EMI) is the transfer of signals between integrated circuits. The need to use external filtering and multiple integrated circuits to complete a given system function increases the opportunities for spurious frequency generation and reception. In addition, the need to use multiple technologies such as MOSFETs for the digital portion and a bipolar or GaAsFET technology for the radio or analog portion of the radio system results in an increased component count leading to increased costs due to area usage, packaging, manufacturing costs, RF shielding requirements, and power distribution difficulties.

One possible solution is to use a single technology to implement the entire radio system. This 'one IC solution' employs the digital MOSFET transistor in an analog RF application so that the signal doesn't need to leave the IC except for reception and transmission.

Although this seems to be the ideal solution, severe technological challenges are preventing the full implementation of the concept. For example, the MOS device has not yet been fully characterized for RF usage, CAD models are not of sufficient accuracy to be used for product quality RF MOS circuits, on-chip filtering capabilities are severely lacking, and crosstalk between digital and analog circuitry on the same substrate and in the same package is significant and is poorly modeled. Although improved transistor and process characterization can ameliorate the first two concerns, the filtering and circuit isolation problems are inherent limitations with current technology capabilities. These effects are manifested as noise injected into oscillators, excess frequencies generated in mixers, parasitic oscillations, low Q filters, increased noise floor, and reduction of overall system sensitivity.

A second compelling economic argument for the investigation into MOSFET technologies is process technology cost. The use of less expensive standard MOS technologies to implement RF analog functions will reduce the cost of individual components in the radio system. This becomes very important for mass produced consumer electronic products as any small reduction in cost can result in major cost savings for the producer.

Regardless of the current technology limitations, the overwhelming economic benefits involved with the single IC solution requires that design methods and practices be generated and tested to provide the ground work for a possible implementation of the concept in the future. Even if the investigations reveal that a single IC solution is not feasible, the economies of scale available with MOS technologies is sufficient to warrant increased

investigation into its RF capabilities. One way to approach this is to investigate RF MOS-FET circuit topologies and capabilities in order to create a background of knowledge and experience in the field.

# 2.2.2 MOSFET Process Technology Background

For many years, MOS technologies have dominated low frequency digital applications. However, with increased demand for faster computing capabilities, MOS technologies were modified and improved to operate faster in the digital environment. With further device enhancements and improved CAD support, MOS devices proved to be highly suitable for the high speed digital processing of analog signals. As this trend of process improvement continues, research into the capabilities of MOS transistors for analog and digital operations at higher frequencies is continuing. Promising results are being shown for filters, ADCs, DACs, dividers, multipliers, counters, PLLs, VCOs, mixers and LNAs [2.2 to 2.16]. Significantly, research has produced exciting results at 1 to 2 GHz for analog operations such as low noise amplifiers, oscillators, and mixers. The frequency of operation for these circuits is expected to increase as device geometries go below the half- and quarter micron level.

As MOS technologies improve, technical challenges are being exposed. Modeling issues not encountered in digital applications such as short channel effects, noise performance, and linearity are becoming obstacles to further exploitation of the high frequency capabilities of the technology[2.17, 2.18]. As transistors are reduced in size to enable higher frequency operation, process variations play a larger role in the reliability of designs and devices deviate significantly from the traditional long gate drain current to

gate voltage square law relationship[2.19]. Greater understanding of the device nonlinearities, 1/f noise, channel noise, short channel effects, doping gradients, gate resistance, parasitic capacitances, and power requirements is needed so as to avoid underestimating or overestimating the capabilities of the process technologies. More accurate process characterization must include RF criteria such as transconductance, noise, port impedances and process variations so that CAD tools can be improved to enhance the accuracy of high frequency analog simulations. As simulation capabilities improve, the margin for error that a designer needs to include in production designs can be reduced, allowing for more aggressive use of the process capabilities, thus avoiding overly conservative design approaches. An improved understanding of MOS technologies will also reveal limitations of the FET device, providing valuable design information to the circuit and system designer. With this knowledge, the design engineer can reduce design cycle time by concentrating on circuit topologies and approaches that will be successful while avoiding fruitless design strategies. Also, the system designer can adjust system level specifications to take full advantage of the capabilities of the technology.

As this research continues, circuit designers need immediate intermediate solutions. A toolkit of design techniques and practices must be developed that can be used to design high frequency MOS circuits with some degree of confidence. Conservative approaches such as using standard low frequency designs modified for higher frequency operation and the transfer of BJT circuit topologies into MOS are good beginnings. High frequency design techniques common with GaAs MESFET or even bipolar technologies are also beneficial, often proving to be directly applicable to new MOS designs. However,

for full technology exploitation, new design methods must be developed specifically for MOS technologies.

MOS technology, with more research and improved design techniques, may prove to be a useful process technology for the high frequency applications in modern communication systems. Although not currently at the maturation level required, it is possible that MOS technologies, fully exploited, may compete technically and economically with bipolar devices for low GHz analog applications.

### 2.3 RFIC Mixer Circuit Topologies

A wide variety of circuits have been used to make mixers. The two main techniques used are the multiplication of the signal with a square wave and the exploitation of device nonlinearities. This discussion will concentrate on the current state of the art in bipolar and FET technologies in a radio frequency integrated circuit environment.

#### 2.3.1 BJT Base and FET Gate Mixers

Conceptually, one of the simplest methods to create a mixer is to use the inherent nonlinearities of a transistor biased as an amplifier. This can be done in almost any technology and is generally based upon creating an amplifier and then modulating the amplifier characteristics at the frequency of the LO. The superposition of two signals onto a device in such as way as to excite the device nonlinearities will produce many extraneous frequency components, only one of which is the desired mixing frequency. Usually, the LO and RF input signals are applied to the base or gate of the transistor after appropriate impedance matching with the IF output signal being extracted from the collector or drain

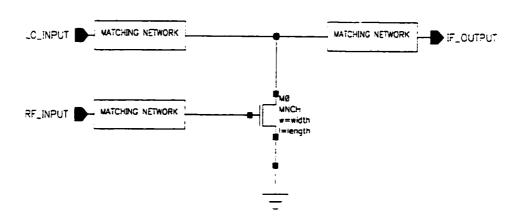

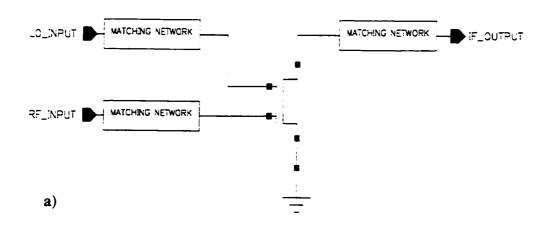

of the transistor after appropriate matching and filtering. Practically, however, it is often difficult to balance all of the design criteria to produce a successful design in the RFIC environment. Usually, adequate linearity and gain are a design trade-off as any technique used to linearize the device reduces the conversion transconductance. In the simple configurations, there is little port isolation and the separation of RF, LO, and IF signals is difficult, often making this technique unsuitable for integration due to the filtering required. A representative circuit, without biasing, is shown in Figure 2.2

Figure 2.2 MOS gate mixer structure

•

#### 2.3.2 Tree or Gilbert Cell Mixers

One of the better integrated mixers is the very common tree mixer, also referred to as the Gilbert cell [2.20]. This circuit is well suited for the RFIC environment and relies upon the co-integration of transistors for its success. It can be singly or fully balanced, and provides inherent port to port isolation which is primarily dependent upon device matching. It can have high linearity and low noise figure with the correct design techniques, usually involving design trade-offs to achieve respectable values. It uses a quad of transistors to switch the gain of an RF amplifier from positive to negative at the frequency of the LO, effectively producing a multiplication between the two signals. This mixer structure can be implemented in almost any transistor technology with varying results. The basic topology is not well suited for reduced power supplies as all devices must be in the active region and a current source is often necessary for biasing. In addition, the operation of the MOS version of this circuit is not optimal as the switching and distortion characteristics of the MOSFET are different from those of the BJT [2.21]. In addition, the parasitic capacitance of the switching devices causes some undesired effects that may impact the high frequency capabilities of the topology. A representative circuit, without biasing, is shown in Figure 2.3.

Figure 2.3 MOS tree mixer structure

#### 2.3.3 FET Drain Mixers

In the linear, or ohmic, region of operation, the FET transistor channel operates as a nonlinear voltage controlled impedance, using the gate-source voltage,  $V_{gs}$ , and the drain-source voltage,  $V_{ds}$ , to control the impedance between the drain and the source. As the device current is then dependent upon two voltages, this nonlinearity allows the use of the device as a mixer by varying the two voltages at different frequencies. One result of this characteristic is the drain mixer, shown in Figure 2.4, in which the RF signal is applied

to the gate and the LO signal is applied to the drain. The resulting IF signal is extracted from the drain with appropriate filtering. This method suffers from similar implementation difficulties as the FET gate and BJT base mixers, and also exhibits significant conversion loss. The usefulness of this mixer is mainly due to the very linear conversion characteristics possible.

Figure 2.4 MOS drain mixer structure

# 2.3.4 FET Ring Mixers

The FET channel impedance characteristics also allow the device to be used as a switch, allowing signals to pass through the device when the channel impedance is low, rejecting signal passage when the impedance is high. This can be used to control the transmission of a signal by a gate control voltage, effectively resulting in the multiplication of the signal with the control voltage. If connected in a ring topology as shown in Figure 2.5, similar in structure and operation to a diode ring mixer, the input RF signal is commutated

to produce the IF signal. This structure can be highly linear but also suffers from similar design constraints as the diode ring mixer such as high LO power requirements, difficulty in port matching, poor port isolation, requirement of baluns at all ports, and conversion loss.

Figure 2.5 MOS ring mixer structure

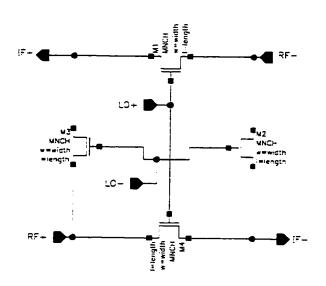

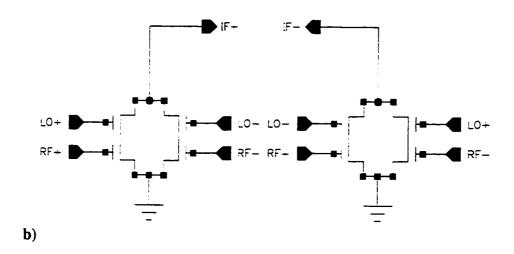

### 2.3.5 FET Dual Gate Mixers

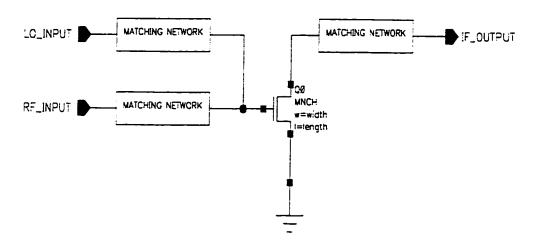

The FET device normally employs one gate to control the channel characteristics. Another form, the dual gate FET or DGFET, uses two gates to accomplish this function providing enhanced functionality and versatility. Depending upon the bias conditions, the DGFET can be used as an amplifier, a mixer, a modulator, or automatic gain control circuit (AGC) among many other uses[2.22 to 2.24]. As a mixer, the LO signal is normally

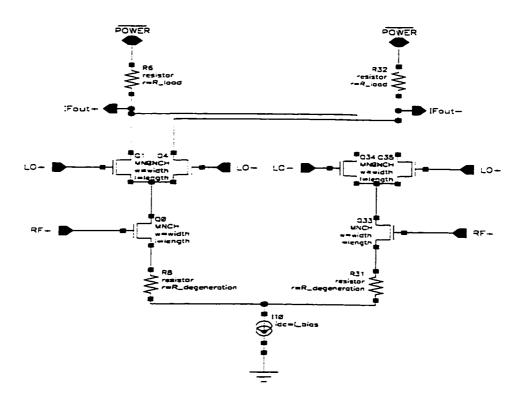

applied to the second, or top, gate, with the RF signal being applied to the first, or lower, gate. This not only provides the best linearity and mixing characteristics, but also allows the use of standard port matching techniques for the RF signal and helps improve the IF to RF port isolation [2.25]. The resulting IF can be recovered at the drain of the composite device after appropriate filtering. In an RFIC environment, suitable balancing structures can obviate or relieve the need for stringent filtering, similar to the tree mixer topologies. The ports of the DGFET are inherently isolated as the LO and RF signals are applied on separate ports and the feedback capacitance between the output and either input is small. In addition, the topology shows great promise for use with reduced power supplies as not all of the devices are biased in the saturation region and there is no inherent need for a current source bias method. Representative circuits, without bias details, are shown in Figure 2.6.

Figure 2.6 a) Unbalanced dual gate mixer structure

b) Balanced dual gate mixer structure

### 2.4 Summary

In order to take advantage of the economic benefits of producing a single IC radio system design or the use of lower cost technologies, research into MOSFET technologies for RF analog applications in the front end of radio systems can be expected to continue.

The design of high performance mixers in an RFIC environment is already a challenge in any technology, but as system complexity increases, the care and innovation required in the design of components such as mixers also increases. The tree or Gilbert cell mixer has been used extensively and is often the first topology used when implementing a MOS version of a high frequency mixer since the design methodology as well as the circuit operation are well understood. In addition, the drain and gate mixer topologies are also well understood, but they are not well suited for RFIC environments due to the low port isolation and filtering requirements. The FET ring topology is often the mixer of choice for high linearity systems but suffers from conversion loss as well as poor port isolation.

The dual gate mixer is the remaining viable option for RFIC mixer design due to inherent port isolation, capability of gain, and low supply voltage capabilities. However, the operation of the device is not well understood and no comprehensive design methods have been reported for use in the RFIC environment. In order to provide another mixer topology option to the RFIC designer and allow greater exploitation of the capabilities of MOS processes for high frequency analog operations, a method to accurately and system-

atically design a dual gate mixer was developed for use in an RFIC or discrete component environment.

# Chapter 3: The Dual Gate FET

#### 3.1 The Dual Gate Structure

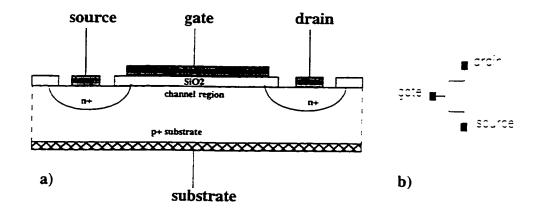

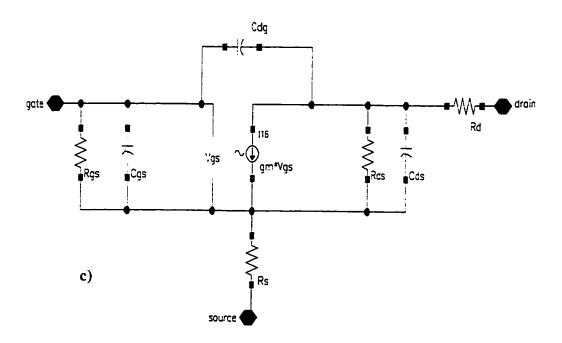

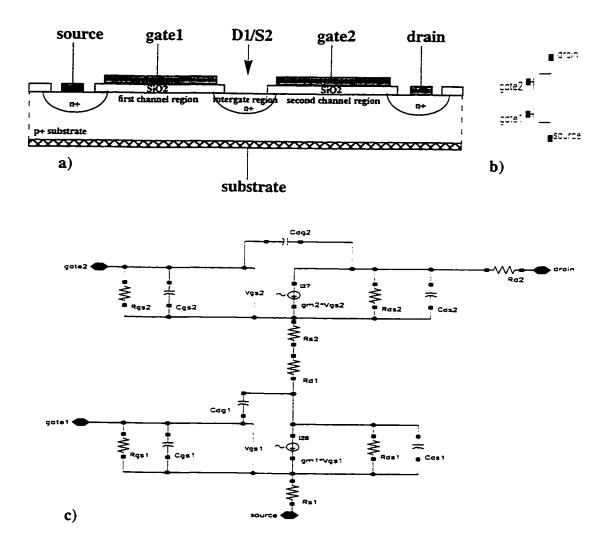

In order to better understand the dual gate structure, Figure 3.1 shows a representative single gate structure consisting of a source, a drain, a gate, and a substrate or bulk connection. The source and drain are n+ diffusion regions with ohmic contacts for connection to other circuitry. The gate consists of a polysilicon material over a thin silicon dioxide layer located over the channel region, the area between the source and drain directly under the gate. The low impedance p+ substrate is used as a reference plane, usually ground, and also serves as the 'back gate' of the channel region. This structure can be shown to have the simplified small signal model shown in Figure 3.1.

The dual gate structure, shown in Figure 3.2, can be seen as an extension of this single gate device. Two gates between the source and drain effectively create two series connected devices with an internal node, labelled D1/S2 in the figure, that simultaneously serves as the drain for one device and the source for the other. A linear small signal model for this device can be formed by the series combination of two single gate small signal models. A generic physical representation and a simplified small signal model are shown in Figure 3.2.

Figure 3.1 a) Generic MOS single gate physical representation

- b) Generic MOS single gate schematic symbol

- c) Simplified MOS single gate small signal model

Figure 3.2 a) Generic MOS dual gate physical representation b) Generic MOS dual gate schematic symbol c) Simplified MOS dual gate small signal model

The use of these small signal models in a mixing application context is somewhat limited due to the highly nonlinear nature of the circuit and to the fact that the excitation of nonlinearities in each device is bias dependent. However, with proper care, linear

models can be used to qualitatively investigate the effects of such characteristics as gate capacitance, port isolation, output impedance, and substrate effects.

## 3.2 Modeling Concerns

## 3.2.1 The Single Gate MOSFET

The current state of the art high frequency models for single gate MOSFETs implemented in CAD simulators do not accurately account for non-ideal device characteristics. Some models do not even calculate the transconductance, output conductance, or the drain current through the transition region between the linear and saturation regions of operation accurately. The current model implementations for such effects as 1/f noise, channel noise, short channel effects, doping gradients, gate resistance, and parasitic capacitances are often insufficient for accurate design and are not generally trusted for production level high frequency analog designs. Tsividis [3.1 to 3.3] provides a valuable overview of various modeling deficiencies in MOSFET models.

This lack of accurate device models can be traced to the history of the MOS-FET and its primary reason for existence, namely low frequency digital applications. If the device is being used as a digital circuit component, essentially being either on or off, with a small transition time between states, then the effects of noise, channel impedance, non-linearities, and gate resistance are not important. As such, there was little incentive to improve the models as the important regions for digital applications were quite sufficiently modeled. As the demand for high speed digital applications increased, the device speed

was increased by scaling the device size, allowing the non-ideal portions of the characteristic to remain hidden in the large signal operation of the digital application.

Only recently has the economic incentive been sufficient to warrant additional research into the full modeling of the MOSFET device, including all effects, in all regions. High quality analog MOSFET models are emerging such as the Nortel MISNAN model [3.4] and new research is continuing[3.5]. With these efforts, more accurate simulation tools are being created in order to enhance the capabilities of the RF MOS designer to create high performance RF MOS analog circuitry.

#### 3.2.2 The Dual Gate MOSFET

Although the dual gate device can be viewed as a series connection of two single gate MOSFET transistors, there are a number of issues specific to the dual gate device that require it to be defined as more than just a 'simple' series connection. Each device of the composite transistor suffers from all of the modeling deficiencies that currently affect single gate devices. In addition, the interconnection of the two devices creates a region of interaction that proves to be difficult to model[3.6,3.7].

In Figure 3.2a, an intergate region is defined as the area between the two channel regions which consists mostly of an n+ doped diffusion. As the RFIC designer often has complete control over the layout of the transistors used, the size of this region depends heavily on the way the transistor is laid out and how the surrounding gates are connected to other circuitry. In addition, the process may not control the doping in this region very closely due to the self aligning properties of many MOS fabrication techniques. As a result, wide variances on the parasitic resistances and capacitances in this region are possible. Depending on the circumstances, these parasitics may or may not be the dominant impediment to improved simulation accuracy.

Due to the topology, each device experiences a different substrate to source voltage which, among other effects, causes the threshold voltage of each device to be different. This effect must be modeled correctly or device characteristics can be grossly distorted in simulation. In addition, the drain current through a device is dependent upon the gate to source voltage,  $v_{gs}$ , as well as the drain to source voltage,  $v_{ds}$ . In this topology, the  $v_{gs}$  for the top device and the  $v_{ds}$  for the bottom device are dependent upon the unknown intergate region voltage and must be solved for numerically by iteration. Although this is not impossible to do, it increases the complexity of the device calculations required and impacts the speed capabilities of the simulation.

As a result of the poor modeling of the conductances in the individual FETs, there is some question as to the effectiveness of the simulation of the interaction of the two devices in the intergate region. Assuming that the RF effects of power transfer depend upon the calculated nodal impedances of the circuit, incorrect conductances at the internal node may cause major errors in simulation. This effect may also depend upon the bias conditions due to the discontinuities in some models between the linear and saturation regions of operation. If the lower device is biased at an inappropriate manner for the simulator, the simulator may produce anomalous circuit responses and the designer may be misled as to the operation of the circuit.

If the DGFET is operated as a small signal amplifier, these modeling effects may be easily avoided by employing appropriate biasing techniques. In a DGFET mixer however, the large signal operation sweeps the operating points of the mixer through the

regions in which the model is deficient. The designer, by using conservative design techniques and relying more upon the currents and voltages that are simulated, and not the derived quantities such as the conductances, can use simulations to provide a means of estimating circuit behaviour.

## 3.2.3 The Cascode Approximation

Although the current MOS models do not inspire much confidence, circuits need to be designed and research must continue. The RF MOS designer can take some positive steps to minimize the detrimental effects of the simulator models currently available.

In the context of dual gate MOSFETs, the designer can minimize the use of special devices, instead relying upon devices more similar in size and shape to the devices that have been characterized for the model. The main result of this is the 'cascode approximation' [3.8 to 3.10] to the dual gate in which all simulations and the physical layouts are done using two separate devices in an explicit series connection of two devices. This allows the use of schematically driven simulation engines without modifications such as special model parameter files, symbols, or model files. In addition, this allows the unmodified use of current layout capabilities such as device extraction, layout vs. schematic (LVS), design rule checking (DRC), as well as parasitic extraction.

In terms of the physical layout, the use of distinct devices to approximate the dual gate may help in a number of ways including ease of layout, improved signal routing, as well as enhanced design reliability. The use of separate devices allows increased care in the layout of each device including substrate contacts, thermal gradients, and number and

location of gates and source and drain contacts. The designer can also increase the separation of the gate circuitry in order to improve port isolation characteristics or to ease the routing of signal or decoupling lines.

The rapid integration of dual gate simulations into the work place can be greatly facilitated by relying upon the simulation environment capabilities currently available. If no user specific files are created, designers can immediately make use of simulator or model upgrades allowing for the highest degree of accuracy and confidence in the design. For these reasons, among others, it is suggested that a suitable design approach to dual gate circuits can be made using the cascode approximation.

### 3.3 Summary

Although the structure of the dual gate device has been shown to be similar in physical construction to the well known single gate device, several effects require that the DGFET be modeled slightly differently than the single gate device. The effects of substrate bias and the intergate region interactions need to be better controlled and more accurately modeled for amplifier or mixer applications.

While the use of the dual gate device for analog applications is currently hampered by the lack of adequate high frequency modeling capabilities, this difficulty is seen to be common to RF MOS devices in general. As the implementation of better high frequency models continues, several suggestions, primarily the use of the cascode approximation, were provided for the RFIC designer to help ameliorate this situation. This provides an interim solution and facilitates the rapid integration of modeling and simulation improvements to the design environment.

# Chapter 4: Design Methodologies

This chapter explains the criteria used in defining a useful engineering design method and explores some of the state of the art design methodologies for dual gate mixers including a short discussion on numerical solution techniques. A theoretical background as well as a concise summary is provided for the proposed method and some of the pertinent features of the method are discussed.

# 4.1 Design Methodology Requirements

An RF design engineer relies upon design methodologies and techniques that have been understood, tried, and confirmed to work. If a design method is inaccurate, cumbersome, or time consuming, it is unlikely to be widely accepted. A good design method helps the engineer design high quality, reliable circuits in the shortest possible amount of time. In order to accomplish this, a good design method should have certain basic qualities. The method should be as simple and accurate as necessary, should provide insight into the operation of the circuit, and be suitable for as wide a variety of situations or circuits as possible. It should not be excessively reliant on computer models and should require a minimum of effort to characterize devices for use in the method.

An engineering design method should only be as simple or as rigorous as necessary. If a method is too simple, inaccuracies result and insufficient information is given to the designer for informed optimization. If the method is too complicated, it may require too much time to implement. If a method involves too many detailed steps, or if the final solution is obscured with excessively detailed mathematical equations, the method may prove to be unwieldy to the designer and be prone to errors or inaccuracies. The price of excessive accuracy may be increased simulation or lab time for a sometimes questionable amount of overall design improvement.

The method should explain or clarify the operation of the circuit to a sufficient degree of detail. This allows the engineer to make informed circuit modifications for intelligent design optimizations. Unknown side effects from uninformed design modification can result in specification failure. Without the required information, the designer must often resort to implementing excessively conservative designs, not realizing the full capabilities of the design.

A useful design methodology is one that can be applied, perhaps with minor modifications, to a wide variety of circuits. Most designers use a 'toolkit' of a limited number of design techniques that have been thoroughly tested and in which they have some degree of confidence. An isolated technique that is difficult to learn and apply does not become part of such a toolkit.

A common problem with RFIC designs is the lack of accurate CAD models for the devices used in the design. Although most device simulation models can predict the current and voltage levels in the devices to a sufficient degree of accuracy, some of the derived quantities such as transconductance or conductance, are very poorly modeled [4.1]. A higher degree of confidence is often given to a design method that does not rely upon these derived quantities. As the designer may have to characterize the devices in the lab before the design can continue, a method that requires a minimum amount of device characterization can significantly reduce design cycle time.

A successful design method should, therefore, be of sufficient rigor and accuracy, should provide information for optimization, have minimal reliance upon CAD tools, and be as flexible as possible.

### 4.2 Current State of the Art

A brief description of the numerical methods used in CAD design tools is provided in order to better understand the theoretical background of some of the mixer design methodologies that are reviewed, followed by brief summaries of some key mixer design approaches to provide a more comprehensive view of the challenges involved in the design procedures.

Following the theoretical background required to explain the proposed design method, the proposed dual gate mixer design procedure for gain and input compression point is outlined and summarized.

# 4.2.1 Harmonic Balance and Large Signal - Small Signal Techniques

The harmonic balance (HB) and large signal-small signal (LS-SS) circuit analysis techniques are used to provide numerical solutions to nonlinear circuits for CAD applications. For a more in depth treatise on these topics, refer to Maas[4.2].

The harmonic balance technique can be viewed as a partitioning of the circuit into linear and nonlinear sections. The nonlinear partition, containing the active devices, is described with equations for the equivalent circuit components and is usually solved using time domain techniques. The linear partition contains the rest of the circuit including, for example, bias and matching circuitry, and is often solved in the frequency domain. The in-

put signals are applied to the circuit and the resulting currents and voltages are calculated in each partition. Conceptually, when the currents and voltages at the interface of the linear and nonlinear partitions match, or are balanced, at all frequencies harmonically related to the input signals, thus 'harmonically balanced', the steady state can be considered achieved, resulting in a numerical solution for the circuit transfer function.

The large signal - small signal (LS-SS) technique is also referred to as conversion matrix analysis and is applicable for nonlinear circuits that have two signal inputs, one being very large compared to the other, and the other being small enough so as to create negligible harmonics in the circuit. This is a situation commonly found in mixer circuits where the LO is large compared to the RF signal and the excess harmonic content caused by the RF signal is small. Initially, the steady state of the complete circuit is found with only the large signal applied, often using HB techniques. Using the steady state results, functions for the nonlinear equivalent circuit components are generated. The nonlinear equivalent circuit model is then converted into a quasi-linear, small signal equivalent circuit, using the derived steady state functions instead of the linear equations for the quasi-linear components. Using linear analysis techniques, equations can then be formulated which provide a numerical solution for the transfer function for the circuit. The application of two signals of different frequencies to a nonlinear circuit will result in the multiplication of the two signals together producing many conversion frequency components. This is represented by the use of matrices instead of scalar values in the linear analysis equations, thus the term 'conversion matrix' analysis.

# 4.2.2 Dual Gate FET Mixer Design Methodologies

Various design methods have been explored for dual gate FET mixers, usually aimed at producing accurate CAD models for design applications and often relying upon variations on the HB or LS-SS numerical analysis methods. Accurate modeling, however, does not always provide the means or method for high performance designs. A few key approaches will be mentioned here as background information for the method proposed in this thesis.

# 4.2.2.1 Dual Gate MOSFET Method: Kleinman

Kleinman's [4.3] method relies upon the understanding that the current and thus the transconductance of the complete dual gate device is a function of both gate biases. Employing a simple equation relating the DC transconductance from each gate to the output as a function of the other gate voltage, the IF frequency components can be isolated and the conversion transconductance,  $g_c$ , can be calculated. This can be seen as a simplification of an analysis based upon a two dimensional Taylor series [4.2]. Kleinman approximates the rather complicated transfer function by ignoring the nonlinearities at each gate and using the linear region of the DC transconductance of each gate to the output.

This method is not difficult to apply but provides no insight into the proper selection of bias points for either the RF or LO ports. As a result, little information is available on how to adjust the bias or LO power conditions to optimize the circuit design. It is, however, aimed at providing a practical design approach for the circuit designer to estimate the conversion gain of the mixer using circuit parameters that are directly available to the designer and are easily measurable.

The concept of treating the dual gate device as a 'multiple entity', where each gate has a separate but codependent function in relation to the output current, is very useful and allows for the characterization of any dual gate device, without having to try and isolate each device separately. The section of the paper concerning gain controlled amplifiers is informative and provides an intuitively appealing description of the operation of the dual gate device. A key portion of this method was the treatment of the transconductance due to the second gate voltage as a separate entity, and not just as a method to modify the transconductance from gate 1 to the output.

## 4.2.2.2 Dual Gate MESFET Method: Tsironis, Meierer, Stahlman

These authors [4.4,4.5] explain a detailed method for the numerical modeling of a DG MESFET device and its use in the design of a mixer. The analysis that is provided is also applicable to MOSFET technologies and provides significant insight into the details of the operation of DG MOSFET devices and, in particular, mixers.

The method of visualizing the usually unavailable drain to source voltage of the bottom device with the aid of a DC nomogram is particularly useful and provides some critical information for the designer. The resulting information concerning the effect of the second gate voltage on the internal operation of the circuit is very revealing. The identification of regions of operation and the descriptions of some of the characteristics of each region is instructive for the selection of bias regions as well as LO signal levels. The investigations into the effects of the external matching circuitry are also very useful and provide

the designer with a considerable wealth of knowledge to draw upon while considering how to interface properly with the mixer. The detailed approach, along with the realistic assumptions and approximations used, provides solid background knowledge for a clearer understanding of the operation of dual gate mixers and permits more informed decision making in the design process.

This method can be considered a type of HB and LS-SS analysis. The individual FET equivalent circuit components are identified and functions are generated for each component. The effects of the LO waveform are assumed and are implicit in the functions that are generated. The treatment of the LO effects on the internal components as a steady state condition and then investigating the RF effects on the overall circuit are key techniques to the success of the method.

Although a design implementation of the method is described, the effort appears to have been aimed more at modeling a specific mixer and confirming the model than providing a general design method. The approach is somewhat complicated, is 'tedious' in its applications [4.5], and requires significant lab work to characterize each device. It must be acknowledged that this work was undertaken in 1983 and significant advances in CAD tools and device modeling, in part due to this work, have occurred since then, possibly reducing the 'tedious' nature of the technique.

### 4.2.2.3 Microwave Mixer Methods: Maas

Maas has published several definitive works [4.6 to 4.8] on nonlinear microwave circuits including the operation of FET mixers, usually focussing on numerical mod-

eling methods and providing significant theoretical detail for the modeling methodologies involved.

The analysis of FET mixers has been identified as a subset of a more general nonlinear analysis approach. Using LS-SS and HB analysis techniques, the operation of MESFET single gate mixers and the methods used to model them are discussed in detail. The extension of these techniques to dual gate devices and a general description of the operation of dual gate devices is also included. While general design guidelines are provided, an in-depth design method for the DGFET is not provided nor suggested.

These numerical methods, meant to provide accurate CAD models, provide improved tools for the designer but are not always directly applicable to the actual design of such mixers. Although the results for a DGFET mixer are provided in final equation form and allow for identification of general trends, they are not directly useful for proper selection of bias points, power levels, nor for a detailed understanding of individual circuits.

The description of the HB and LS-SS approaches found in this work [4.7] is a major portion of the theoretical underpinnings of the method described in this thesis.

# 4.2.3 Drain Mixer Methodologies

Drain mixer design methods are useful to investigate because it is possible to view the DGFET mixer as a variation of the drain mixer. Considering the bottom device as the mixing element, the top device can be seen to be the means of applying the LO to the drain as well as being a common gate amplifier stage for the extraction of the IF signal. As

the mixing action in both types of mixers occurs in a similar manner, drain mixer topologies can be instructional in DGFET mixer designs as well.

# 4.2.3.1 MESFET Drain Mixer Method: Begemann, Jacob

This numerical method [4.9] is also a type of HB and LS-SS analysis. It uses an equivalent circuit for the FET in the linear operation region, identifies the effect of the LO waveform on each component, and creates functions for all of the individual components. Linear analysis techniques are used to create the required matrix equations to calculate the mixer characteristics.

The separation of the frequency components using ideal filters, similar to Pucel's treatment with gate mixers [4.10], is insightful and allows the designer to view the circuit in a variety of ways, depending on which frequency component is being investigated.

An interesting conclusion drawn in this paper is that the drain to source channel resistance,  $R_{ds}$ , is not a major contributing factor to the overall conversion gain, while the dominating factor is the device transconductance itself.

Although the paper concentrates on the theoretical analysis of the mixing processes in a drain mixer, the mixing process itself is very similar to that of the DGFET in one region of its operation, providing a deeper understanding of the DGFET mixing action. However, little insight into the proper selection of RF or LO bias points or LO power level requirements is provided.

# 4.2.3.2 MESFET Drain Mixer Method: Cayrou, Gayral, Graffeuil...

This analysis [4.11], also just for drain mixers, is very similar to the one by Begemann and Jacob but differs slightly in the mathematical approach. The separation of the effects of the transconductance and the channel conductance provides a means to calculate the effect of each separately. This provides a means of simplification of the final result and helps identify the main contributions to the mixing process. The authors used the HB technique to confirm the theory by simulation.